· Flash ROM - объем энергонезависимой памяти программ (в килобайтах);

· EEPROM - объем энергонезависимой памяти данных (в байтах);

· RAM - объем статической памяти данных (в байтах);

· External RAM - возможность подключения к микроконтроллеру дополнительной микросхемы внешней статической памяти данных (в килобайтах);

· ISP - возможность программирования микроконтроллера в системе (на целевой плате) при основном напряжении питания;

· SPM - функция самопрограммирования Flash ROM памяти микроконтроллера в системе без участия внешнего программатора;

· JTAG - встроенный JTAG - интерфейс;

· I/O (pins) - максимальное количество доступных линий ввода / вывода;

· Timer(s) 8/16 bit - количество и разрядность таймеров/счетчиков;

· USI - универсальный коммуникационный интерфейс;

· AC - аналоговый компаратор;

· ADC (channels) - количество каналов аналого-цифрового преобразования;

· Internal RC - наличие внутренней RC-цепочки для автономной работы микроконтроллера (без внешнего источника опорной частоты);

· WDT - сторожевой таймер;

· BDC - аппаратный программируемый блок защиты от сбоев при внезапном (в том числе и кратковременном) пропадании напряжения питания микроконтроллера;

· UART - асинхронный последовательный приемопередатчик;

· SPI - синхронный трехпроводной последовательный интерфейс;

· I2C - двухпроводной последовательный интерфейс;

· RTC - система реального времени;

· PWM (channels) - количество независимых каналов широтно - импульсной модуляции;

Все AVR имеют Flash-память программ, которая может быть загружена как с помощью обычного программатора, так и с помощью SPI-интерфейса, в том числе непосредственно на целевой плате. Число циклов перезаписи - не менее 1000. Последние версии кристаллов имеют возможность самопрограммирования. Это означает, что микроконтроллер способен самостоятельно, без какого-либо внешнего программатора, изменять содержимое ячеек памяти программ. То есть, новые AVR могут менять алгоритмы своего функционирования и программы, заложенные в них, и далее работать уже по измененному алгоритму или новой программе. Например, Вы можете написать и сохранить несколько рабочих версий программы для конкретного приложения во внешней энергонезависимой памяти (DataFlash, SEEPROM и т.п.), а затем по мере необходимости или по реакции на какие-нибудь внешние или внутренние логические условия перегружать рабочие программы в тот же самый микроконтроллер AVR, не извлекая его из печатной платы. Для этого весь массив памяти программ делится на две неравные по объему области: блок загрузчика (программа, управляющая перезаписью Flash-памяти программ) и блок для размещения рабочего программного кода, причем свободная память в области загрузчика может быть использована в качестве дополнительного пространства для рабочего кода. Программа - загрузчик создается самим разработчиком и должна быть запрограммирована внешним программатором.

Все AVR имеют также блок энергонезависимой электрически стираемой памяти данных EEPROM. Этот тип памяти, доступный программе микроконтроллера непосредственно в ходе ее выполнения, удобен для хранения промежуточных данных, различных констант, таблиц перекодировок, калибровочных коэффициентов и т.п. EEPROM также может быть загружена извне как через SPI интерфейс, так и с помощью обычного программатора. Число циклов перезаписи - не менее 100000. Два программируемых бита секретности позволяют защитить память программ и энергонезависимую память данных EEPROM от несанкционированного считывания. Внутренняя оперативная память SRAM имеется у всех AVR семейств "classic" и "mega" и у одного нового кристалла семейства "tiny" - ATtiny26/L. Для некоторых микроконтроллеров возможна организация подключения внешней памяти данных объемом до 64К.

Внутренний тактовый генератор AVR может запускаться от нескольких источников опорной частоты (внешний генератор, внешний кварцевый резонатор, внутренняя или внешняя RC-цепочка). Поскольку AVR-микроконтроллеры полностью статические, минимальная допустимая частота ничем не ограничена (вплоть до пошагового режима). Максимальная рабочая частота определяется конкретным типом микроконтроллера. Интересную аппаратную особенность имеет микроконтроллер ATtiny15L. Он содержит блок PLL для аппаратного умножения основной тактовой частоты в 16 раз. При номинальном значении последней 1,6 МГц получаемая вспомогательная периферийная частота равна 25,6 МГц. Эта частота может служить источником для одного из таймеров/счетчиков микроконтроллера, значительно повышая временное разрешение его работы.

Сторожевой (WATCHDOG) таймер предназначен для защиты микроконтроллера от сбоев в процессе работы. Он имеет свой собственный RC-генератор, работающий на частоте 1 МГц. Эта частота является приближенной и зависит прежде всего от величины напряжения питания микроконтроллера и от температуры. WATCHDOG-таймер снабжен своим собственным предделителем входной частоты с программируемым коэффициентом деления, что позволяет подстраивать временной интервал переполнения таймера и сброса микроконтроллера. WATCHDOG-таймер может быть отключен программным образом во время работы микроконтроллера как в активном режиме, так и в любом из режимов пониженного энергопотребления. В последнем случае это приводит к значительному снижению потребляемого тока.

Микроконтроллеры AVR имеют в своем составе от 1 до 4 таймеров/счетчиков общего назначения с разрядностью 8 или 16 бит, которые могут работать и как таймеры от внутреннего источника опорной частоты, и как счетчики внешних событий с внешним тактированием. Общие черты всех таймеров/счетчиков следующие.

· наличие программируемого предделителя входной частоты с различными градациями деления. Отличительной чертой является возможность работы таймеров/счетчиков на основной тактовой частоте микроконтроллера без предварительного ее понижения, что существенно повышает точность генерации временных интервалов системы;

· независимое функционирование от режима работы процессорного ядра микроконтроллера (т.е. они могут быть как считаны, так и загружены новым значением в любое время);

· возможность работы или от внутреннего источника опорной частоты, или в качестве счетчика событий. Верхний частотный порог определен в этом случае как половина основной тактовой частоты микроконтроллера. Выбор перепада внешнего источника (фронт или срез) программируется пользователем;

· наличие различных векторов прерываний для нескольких различных событий (переполнение, захват, сравнение).

Система реального времени (RTC) реализована во всех микроконтроллерах семейства "mega" и в двух кристаллах семейства "classic" - AT90(L)S8535. Таймер/счетчик RTC имеет свой собственный предделитель, который может быть программным способом подключен или к основному внутреннему источнику тактовой частоты микроконтроллера, или к дополнительному асинхронному источнику опорной частоты (кварцевый резонатор или внешний синхросигнал). Для этой цели зарезервированы два внешних вывода микроконтроллера. Внутренний осциллятор, нагруженный на счетный вход таймера/счетчика RTC, оптимизирован для работы с внешним "часовым" кварцевым резонатором 32,768 кГц.

Порты ввода/вывода AVR имеют число независимых линий "Вход/Выход" от 3 до 53. Каждый разряд порта может быть запрограммирован на ввод или на вывод информации. Мощные выходные драйверы обеспечивают токовую нагрузочную способность 20 мА на линию порта (втекающий ток) при максимальном значении 40 мА, что позволяет, например, непосредственно подключать к микроконтроллеру светодиоды и биполярные транзисторы. Общая токовая нагрузка на все линии одного порта не должна превышать 80 мА (все значения приведены для напряжения питания 5 В).

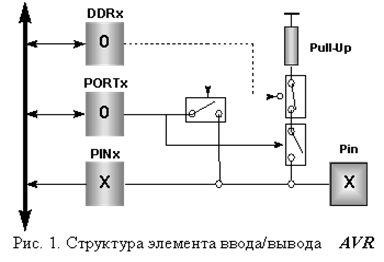

Интересная архитектурная особенность построения портов ввода/вывода у AVR заключается в том, что для каждого физического вывода существует 3 бита контроля/управления, а не 2, как у распространенных 8-разрядных микроконтроллеров (Intel, Microchip, Motorola и т.д.). Упрощенная структурная схема элемента ввода/вывода AVR - микроконтроллера приведена на рис. 1. Здесь DDRx - бит контроля направления передачи данных и привязки вывода к шине питания (VCC), PORTx - бит привязки вывода к VCC и бит выходных данных, PINx - бит для отображения логического уровня сигнала на физическом выводе микросхемы.

Естественно возникает вопрос: а зачем необходимы именно 3 бита? Дело в том, что использование только двух бит контроля/управления порождает ряд проблем при операциях типа "чтение-модификация-запись". Например, если имеют место две последовательные операции "чтение-модификация-запись", то первый результат может быть потерян безвозвратно, если вывод порта работает на емкостную нагрузку и требуется некоторое время для стабилизации уровня сигнала на внешнем выводе микросхемы. Архитектура построения портов ввода/вывода AVR с тремя битами контроля/управления позволяет разработчику полностью контролировать процесс ввода/вывода. Если необходимо получить реальное значение сигнала на физическом выводе микроконтроллера - читайте содержимое бита по адресу PINx. Если требуется обновить выходы - прочитайте PORTx защелку и потом модифицируйте данные. Это позволяет избежать необходимости иметь копию содержимого порта в памяти для безопасности и повышает скорость работы микроконтроллера при работе с внешними устройствами. Особую значимость приобретает данная возможность AVR для реализации систем, работающих в условиях внешних электрических помех.

Аналоговый компаратор входит в состав большинства микроконтроллеров AVR. Типовое напряжение смещения равно 10 мВ, время задержки распространения составляет 500 нс и зависит от напряжения питания микроконтроллера. Так, например, при напряжении питания 2,7 Вольт оно равно 750 нс. Аналоговый компаратор имеет свой собственный вектор прерывания в общей системе прерываний микроконтроллера. При этом тип перепада, вызывающий запрос на прерывание при срабатывании компаратора, может быть запрограммирован пользователем как фронт, срез или переключение. Логический выход компаратора может быть программным образом подключен ко входу одного из 16-разрядных таймеров/счетчиков, работающего в режиме захвата. Это дает возможность измерять длительность аналоговых сигналов а также максимально просто реализовывать АЦП двухтактного интегрирования.

Аналого - цифровой преобразователь (АЦП) построен по классической схеме последовательных приближений с устройством выборки/хранения (УВХ). Каждый из аналоговых входов может быть соединен со входом УВХ через аналоговый мультиплексор. Устройство выборки/хранения имеет свой собственный усилитель, гарантирующий, что измеряемый аналоговый сигнал будет стабильным в течение всего времени преобразования. Разрядность АЦП составляет 10 бит при нормируемой погрешности +/- 2 разряда. АЦП может работать в двух режимах - однократное преобразование по любому выбранному каналу и последовательный циклический опрос всех каналов. Время преобразования выбирается программно с помощью установки коэффициента деления частоты специального предделителя, входящего в состав блока АЦП. Оно составляет 70...280 мкс для ATmega103 и 65...260 мкс для всех остальных микроконтроллеров, имеющих в своем составе АЦП. Важной особенностью аналого-цифрового преобразователя является функция подавления шума при преобразовании. Пользователь имеет возможность, выполнив короткий ряд программных операций, запустить АЦП в то время, когда центральный процессор находится в одном из режимов пониженного энергопотребления. При этом на точность преобразования не будут оказывать влияние помехи, возникающие при работе процессорного ядра.

AVR - микроконтроллеры могут быть переведены программным путем в один из шести режимов пониженного энергопотребления. Для разных семейств AVR и разных микроконтроллеров в пределах каждого семейства изменяются количество и сочетание доступных режимов пониженного энергопотребления. Подробную информацию можно найти в оригинальной технической документации Atmel Corp.

· Режим холостого хода (IDLE), в котором прекращает работу только процессор и фиксируется содержимое памяти данных, а внутренний генератор синхросигналов, таймеры, система прерываний и WATCHDOG-таймер продолжают функционировать.

· Режим микропотребления (Power Down), в котором сохраняется содержимое регистрового файла, но останавливается внутренний генератор синхросигналов. Выход из Power Down возможен либо по общему сбросу микроконтроллера, либо по сигналу (уровень) от внешнего источника прерывания. При включенном WATCHDOG-таймере ток потребления в этом режиме составляет около 60...80 мкА, а при выключенном - менее 1 мкА для всех типов AVR. Вышеприведенные значения справедливы для величины питающего напряжения 5 В.

· Режим сохранения энергии (Power Save), который реализован только у тех AVR, которые имеют в своем составе систему реального времени. В основном, режим Power Save идентичен Power Down, но здесь допускается независимая работа дополнительного таймера/счетчика RTC. Выход из режима Power Save возможен по прерыванию, вызванному или переполнением таймера/счетчика RTC, или срабатыванием блока сравнения этого счетчика. Ток потребления в этом режиме составляет 6...10 мкА при напряжении питания 5 В на частоте 32,768 кГц.

· Режим подавления шума при работе аналого-цифрового преобразователя (ADC Noise Reduction). Как уже отмечалось, в этом режиме останавливается процессорное ядро, но разрешена работа АЦП, двухпроводного интерфейса I2C и сторожевого таймера.

· Основной режим ожидания (Standby). Идентичен режиму Power Down, но здесь работа тактового генератора не прекращается. Это гарантирует быстрый выход микроконтроллера из режима ожидания всего за 6 тактов генератора.

· Дополнительный режим ожидания (Extended Standby). Идентичен режиму Power Save, но здесь работа тактового генератора тоже не прекращается. Это гарантирует быстрый выход микроконтроллера из режима ожидания всего за 6 тактов генератора.

Микроконтроллеры AVR mega64, mega103 и mega128 имеют еще одну примечательную архитектурную особенность, позволяющую значительно снизить энергопотребление всего кристалла в целом, когда в процессе работы возникают вынужденные паузы ожидания. В этом случае целесообразно уменьшить ток потребления центрального процессора и периферийных устройств как в активном режиме, так и в режиме холостого хода, понизив основную тактовую частоту микроконтроллера. Для этой цели на кристалле размещен специальный предделитель, позволяющий делить основную тактовую частоту на целое число в диапазоне от 2 до 129. Включение/выключение данной функции осуществляется одной короткой командой в программе.

AVR функционируют в широком диапазоне питающих напряжений от 1,8 до 6,0 Вольт. Энергопотребление в активном режиме зависит от величины напряжения питания, от частоты, на которой работает AVR и от конкретного типа микроконтроллера. Подробные спецификации обычно приводятся в оригинальной технической документации Atmel Corp. Температурные диапазоны работы микроконтроллеров AVR - коммерческий (0С...70С) и индустриальный (-40С...+85С). К сожалению, корпорация Atmel не выпускает и не планирует выпускать AVR для работы в автомобильном (-40С...+125С) и военном (-55С...+125С) температурных диапазонах.

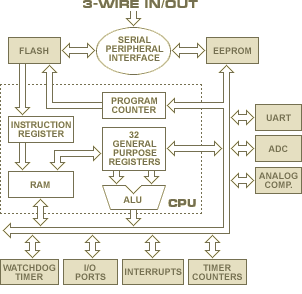

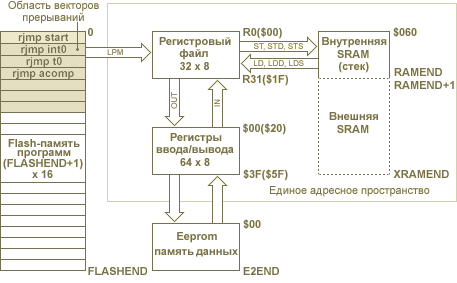

Рис. 2: Структурная схема AVR.

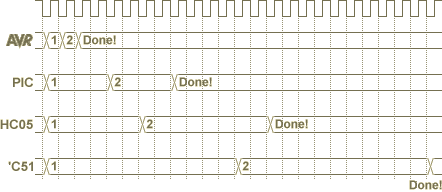

С точки зрения программиста AVR представляет собой 8-разрядный RISC микроконтроллер, имеющий быстрый Гарвардский процессор, память программ, память данных, порты ввода/вывода и различные интерфейсные схемы. Структурная схема микроконтроллера приведена на рис. 2. Гарвардская архитектура AVR реализует полное логическое и физическое разделение не только адресных пространств, но и информационных шин для обращения к памяти программ и к памяти данных, причем способы адресации и доступа к этим массивам памяти также различны. Подобное построение уже ближе к структуре цифровых сигнальных процессоров и обеспечивает существенное повышение производительности. Центральный процессор работает одновременно как с памятью программ, так и с памятью данных; разрядность шины памяти программ расширена до 16 бит. Следующим шагом на пути увеличения быстродействия AVR является использование технологии конвейеризации, вследствие чего цикл "выборка - исполнение" команды заметно сокращен. Например, у микроконтроллеров семейства MCS51 короткая команда выполняется за 12 тактов генератора (1 машинный цикл), в течение которого процессор последовательно считывает код операции и исполняет ее. В PIC-контроллерах фирмы Microchip, где уже реализован конвейер, короткая команда выполняется в течение 8 периодов тактовой частоты (2 машинных цикла). За это время последовательно дешифрируется и считывается код операции, исполняется команда, фиксируется результат и одновременно считывается код следующей операции (одноуровневый конвейер). Поэтому в общем потоке команд одна короткая команда реализуется за 4 периода тактовой частоты или за один машинный цикл. В микроконтроллерах AVR тоже используется одноуровневый конвейер при обращении к памяти программ и короткая команда в общем потоке выполняется, как и в PIC-контроллерах, за один машинный цикл. Главное же отличие состоит в том, что этот цикл у AVR составляет всего один период тактовой частоты. Для сравнения, на рис. 3 приведены временные диаграммы при выполнении типовой команды для различных микроконтроллерных платформ.

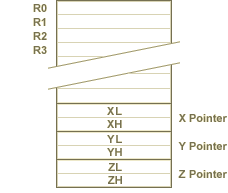

Следующая отличительная черта архитектуры микроконтроллеров AVR - регистровый файл быстрого доступа, структурная схема которого показана на рис. 4. Каждый из 32-х регистров общего назначения длиной 1 байт непосредственно связан с арифметико-логическим устройством (ALU) процессора. Другими словами, в AVR существует 32 регистра - аккумулятора (сравните, например, с MCS51). Это обстоятельство позволяет в сочетании с конвейерной обработкой выполнять одну операцию в ALU за один машинный цикл. Так, два операнда извлекаются из регистрового файла, выполняется команда и результат записывается обратно в регистровый файл в течение только одного машинного цикла.

Рис. 3: Сравнительная характеристика некоторых микропроцессорных платформ.

Шесть из 32-х регистров файла могут использоваться как три 16-разрядных указателя адреса при косвенной адресации данных. Один из этих указателей (Z Pointer) применяется также для доступа к данным, записанным в памяти программ микроконтроллера. Использование трех 16-битных указателей (X, Y и Z Pointers) существенно повышает скорость пересылки данных при работе прикладной программы.

Рис. 4: Регистровый файл.

Регистровый файл занимает младшие 32 байта в общем адресном пространстве SRAM AVR. Такое архитектурное решение позволяет получать доступ к быстрой "регистровой" оперативной памяти микроконтроллера двумя путями - непосредственной адресацией в коде команды к любой ячейке и другими способами адресации ячеек SRAM. В технической документации фирмы Atmel это полезное свойство носит название "быстрое контекстное переключение" и является еще одной отличительной особенностью архитектуры AVR, повышающей эффективность работы микроконтроллера и его производительность. Особенно заметно данное преимущество при реализации процедур целочисленной 16-битной арифметики, когда исключаются многократные пересылки между различными ячейками памяти данных при обработке арифметических операндов в ALU.

Система команд AVR весьма развита и насчитывает до 133 различных инструкций. Конкретное количество команд для каждого микроконтроллера того или иного семейства AVR приведено в таблицах 1 - 2. Почти все команды имеют фиксированную длину в одно слово (16 бит), что позволяет в большинстве случаев объединять в одной команде и код операции, и операнд(ы). Лишь немногие команды имеют размер в 2 слова (32 бит) и относятся к группе команд вызова процедуры CALL, длинных переходов в пределах всего адресного пространства JMP, возврата из подпрограмм RET и команд работы с памятью программ LPM. Различают пять групп команд AVR: условного ветвления, безусловного ветвления, арифметические и логические операции, команды пересылки данных, команды работы с битами. В последних версиях кристаллов AVR семейства "mega" реализована функция аппаратного умножения, что придает новым микроконтроллерам еще больше привлекательности с точки зрения разработчика.

По разнообразию и количеству реализованных инструкций AVR больше похожи на CISC, чем на RISC процессоры. Например, у PIC-контроллеров система команд насчитывает до 75 различных инструкций, а у MCS51 она составляет 111. В целом, прогрессивная RISC архитектура AVR в сочетании с наличием регистрового файла и расширенной системы команд позволяет в короткие сроки создавать работоспособные программы с эффективным кодом как по компактности реализации, так и по скорости выполнения.

Корпорация Atmel планирует дальнейшее развитие перспективной линии AVR - микроконтроллеров. Исключение составляет лишь семейство "classic", развитие которого не планируется. Считается, что это семейство функционально сбалансировано и разнообразно представлено. В семействе "tiny" анонсирован очень интересный микроконтроллер - ATtiny26, имеющий в своем составе блок SRAM емкостью 128 байт и модуль USI (Universal Serial Interface). Это означает, что один и тот же периферийный узел связи на кристалле может быть программным образом сконфигурирован для работы в качестве коммуникационных интерфейсов SPI (Master/Slave) или I2C (Master/Slave). Дополнительно USI может быть запрограммирован для работы в качестве полудуплексного UART или 4/12 разрядного счетчика. Но наиболее интересные решения реализованы в семействе "mega", где анонсирован и начат серийный выпуск целого ряд кристаллов, которые будут выпускаться по технологии 0,35 мкм. Объем Flash-памяти программ с функциями ISP и SPM у новых "mega" будет варьироваться от 8 до 128 килобайт, а выпускаться они будут в корпусах MLF, DIP и TQFP с количеством выводов от 32 до 64. Все новые микроконтроллеры семейства "mega" будут иметь JTAG - интерфейс (за исключением mega8), аппаратный умножитель 8х8, дающий 16-разрядный результат, схему защиты от сбоев, двухпроводной последовательный интерфейс, аналого-цифровой преобразователь (за исключением ATmega162) и ряд других аппаратных особенностей (см. таблицу 3). Помимо этого, вдвое будет повышена скорость работы всех периферийных узлов (SPI, PWM, UART и др.), улучшена работа схемы тактирования и упрощен доступ к внешней памяти данных.

Улучшенная RISC (enhanced RISC) архитектура AVR-микроконтроллеров (рис. 2) объединяет в себе комплекс решений, направленных на повышение быстродействия микропроцессорного ядра AVR.

Арифметико-логическое устройство (ALU), в котором выполняются все вычислительные операции, имеет доступ к 32-м оперативным регистрам, объединенным в регистровый файл. Выборка содержимого регистров, выполнение операции и запись результата обратно в регистровый файл выполняются за один машинный цикл. Для сравнения полезно вспомнить, что большинство встраиваемых микроконтроллеров имеют только один такой регистр, непосредственно доступный ALU, - аккумулятор, что требует включения в программу дополнительных команд его загрузки и считывания.

Основной идеей всех RISC (Reduced Instruction Set Computer), как известно, является увеличение быстродействия за счет сокращения количества операций обмена с памятью программ. Для этого каждую команду стремятся уместить в одну ячейку памяти программ. При ограниченной разрядности ячейки памяти это неизбежно приводит к сокращению набора команд микропроцессора.

У AVR-микроконтроллеров в соответствии с этим принципом практически все команды (исключая те, у которых одним из операндов является 16-разрядный адрес) также упакованы в одну ячейку памяти программ. Но сделать это удалось не за счет сокращения количества команд процессора, а путем расширения ячейки памяти программ до 16 разрядов. Такое решение является причиной богатства системы команд AVR по сравнению с другими RISC-микроконтроллерами.

Организация памяти AVR выполнена по схеме Гарвардского типа, в которой разделены не только адресные пространства памяти программ и памяти данных, но также и шины доступа к ним.

Вся программная память AVR-микроконтроллеров выполнена по технологии FLASH и размещена на кристалле. Она представляет собой последовательность 16-разрядных ячеек и имеет емкость от 512 слов до 64K слов в зависимости от типа кристалла.

Во FLASH-память, кроме программы, могут быть записаны постоянные данные, которые не изменяются во время функционирования микропроцессорной системы. Это различные константы, таблицы знакогенераторов, таблицы линеаризации датчиков и т. п.

Достоинством технологии FLASH является высокая степень упаковки, а недостатком то, что она не позволяет стирать отдельные ячейки. Поэтому всегда выполняется полная очистка всей памяти программ. При этом для AVR гарантируется, как минимум, 1000 циклов перезаписи FLASH-памяти.

Кроме того, для хранения данных AVR-микроконтроллеры могут иметь, в зависимости от типа кристалла, внутреннюю (от 0 до 4K байт) и внешнюю (от 0 до 64 Кбайт) оперативную SRAM память и энергонезависимую внутреннюю EEPROM память (от 0 до 4K байт).

Разделение шин доступа (рис. 2) к FLASH памяти и SRAM памяти дает возможность иметь шины данных для памяти данных и памяти программ различной разрядности а также использовать технологию конвейеризации. Конвейеризация заключается в том, что во время исполнения текущей команды программный код следующей уже выбирается из памяти и дешифрируется.

Для сравнения вспомним, что у микроконтроллеров семейства MCS-51 выборка кода команды и ее исполнение осуществляются последовательно, что занимает один машинный цикл, который длится 12 периодов кварцевого резонатора.

В случае использования конвейера приведенную длительность машинного цикла можно сократить. Например, у PIC-микроконтроллеров фирмы Microchip за счет использования конвейера удалось уменьшить длительность машинного цикла до 4 периодов кварцевого резонатора. Длительность же машинного цикла AVR составляет один период кварцевого резонатора. Таким образом, AVR способны обеспечивать заданную производительность при более низкой тактовой частоте. Именно эта особенность архитектуры и позволяет AVR-микроконтроллерам иметь наилучшее соотношение энергопотребление/производительность, так как потребление КМОП микросхем, как известно, определяется их рабочей частотой.

EEPROM блок электрически стираемой памяти AVR предназначен для хранения энергонезависимых данных, которые могут изменяться непосредственно на объекте. Это калибровочные коэффициенты, различные уставки, конфигурационные параметры системы. EEPROM-память имеет меньшую, по сравнению с FLASH, емкость (до 4К байт), но при этом допускает возможность побайтной перезаписи ячеек, которая может происходить как под управлением внешнего процессора, так и под управлением собственно AVR-микроконтроллера во время его работы по программе.

Программирование энергонезависимых блоков памяти AVR может осуществляться как параллельно, так и последовательно через SPI (Serial Peripheral Interface) интерфейс.

Управление и обмен данными с EEPROM-памятью и со всеми периферийными узлами осуществляется при помощи регистров ввода/вывода, которые имеются в каждом периферийном узле

Так же, как и у других встраиваемых микроконтроллеров, система команд АVR (см. Таблицу 1 в Приложении) включает команды арифметических и логических операций, команды передачи данных, команды, управляющие последовательностью выполнения программы и команды операций с битами.

Имея 16-разрядную ячейку памяти программ, AVR отличаются богатством своей системы команд по сравнению с другими RISC-микроконтроллерами.

Для удобства написания и анализа программ всем операциям из системы команд помимо двоичного кода сопоставлены мнемокоды ассемблера (символические обозначения операций), которые используются при создании исходного текста программы. Специальные программы-трансляторы переводят затем символические обозначения в двоичные коды.

Система команд AVR микроконтроллеров, приведенная в Таблице 1, содержит 121 инструкцию и применима без каких-либо оговорок для микроконтроллера ATmega103.

Младшие модели AVR не имеют некоторых команд из приведенного списка. Основное отличие заключается в том, что те микроконтроллеры (AT90S1200, ATtiny10/11), у которых отсутствует SRAM, не содержат и соответствующих команд работы с оперативной памятью. Кроме того, AT90S1200 не имеет команд ADIW, SBIW, IJMP, ICALL, LPM, а ATtiny10/11 - команд ADIW, SBIW, IJMP, ICALL.

Только MegaAVR имеют двухсловные, выполняемые за три такта, команды абсолютных переходов JMP и CALL. Всем остальным типам AVR (Tiny и Classic) эти медленные команды не нужны, так как все адресное пространство объемом до 4K слов достижимо при помощи команд относительных переходов RJMP, RCALL.

Также особняком стоит команда ELPM страничного чтения FLASH памяти, которая существует и необходима только для ATmega103 и ATmega128 ввиду увеличения размеров памяти программ у этих микроконтроллеров до 128K байт.

Подсчитывая количество инструкций в системе команд AVR, видимо следует обратить внимание на то, что для двух команд из группы арифметических операций существует по два мнемокода. Мнемокоды ANDI и CBR а также ORI и SBR дублируют друг друга, то есть транслируются в один и тот же двоичный код. Выбор между ними программист может выполнять произвольно в зависимости от контекста программы.

Таким образом, AVR-микроконтролеры в зависимости от типа имеют 89 / 90 / 118 / 121 мнемокодов или 87 / 88 / 116 / 119 различных двоичных кодов команд.

Специальная директива ассемблера

.device <типAVR>обеспечивает контроль соответствия команд, используемых в тексте программы, типу указанного процессора.

При переходе от младших к старшим моделям AVR существует совместимость в смысле системы команд, однако необходимо помнить, что адреса векторов прерывания одних и тех же периферийных узлов у различных типов AVR различны, что требует внесения соответствующих изменений в программу при ее переносе на другой тип AVR.

На рисунке 5 изображена программная модель AVR-микроконтроллеров, которая представляет собой диаграмму программно доступных ресурсов AVR. Центральным блоком на этой диаграмме является регистровый файл на 32 оперативных регистра (R0-R31), непосредственно доступных ALU. Старшие регистры (рис. 4) объединены парами и образуют три 16-разрядных регистра, предназначенных для косвенной адресации ячеек памяти (AVR без SRAM имеют только один 16-битный регистр Z).

Рис. 5: Программная модель AVR-микроконтроллеров.

Все арифметические и логические операции а также часть операций работы с битами (см. таблицу 1) выполняются в ALU только над содержимым оперативных регистров. Следует обратить внимание, что команды, которые в качестве второго операнда имеют константу (SUBI, SBCI, ANDI, ORI, SBR, CBR), могут использовать в качестве первого операнда только регистры из второй половины регистрового файла (R16-R31). Команды 16-разрядного сложения с константой ADIW и вычитания константы SBIW в качестве первого операнда используют только регистры R24, R26, R28, R30.

Во время выполнения арифметических и логических операций или операций работы с битами ALU формирует те или иные (см. таблицу 1) признаки результата операции, то есть устанавливает или сбрасывает биты в регистре состояния SREG (Status Register) (рис.6).

| I | T | H | S | V | N | Z | C |

Рис. 6: Регистр состояния SREG (Status Register).

· Бит С (carry) устанавливается, если во время выполнения операции был перенос из старшего разряда результата;

· Бит Z (zero) устанавливается, если результат операции равен 0;

· Бит N устанавливается, если MSB (Most Significant Bit - старший бит) результата равен 1 (правильно показывает знак результата, если не было переполнения разрядной сетки знакового числа);

· Бит V устанавливается, если во время выполнения операции было переполнение разрядной сетки знакового результата;

· Бит S = N + V (правильно показывает знак результата и при переполнении разрядной сетки знакового числа);

· Бит H устанавливается, если во время выполнения операции был перенос из 3-го разряда результата.

Признаки результата операции могут быть затем использованы в программе для выполнения дальнейших арифметико-логических операций или команд условных переходов.

Для хранения оперативных данных программист, кроме регистрового файла, может использовать внутреннюю и внешнюю (если они имеются) блоки SRAM (рис. 5).

Работа с внешней SRAM может быть программно разрешена/запрещена установкой/сбросом бита SRE в регистре ввода/вывода MCUSR.

Операции обмена с внутренней оперативной памятью AVR-микроконтроллер выполняет за два машинных цикла. Доступ к внешней SRAM требует одного дополнительного цикла на каждый байт по сравнению с внутренней памятью. Кроме того, установкой бита SRW в регистре ввода/вывода MCUSR можно программно увеличить время обмена с внешней SRAM еще на один дополнительный машинный цикл ожидания.

Выполнять арифметико-логические операции и операции сдвига непосредственно над содержимым ячеек памяти нельзя. Нельзя также записать константу или очистить содержимое ячейки памяти. Система команд AVR позволяет лишь выполнять операции обмена данными между ячейками SRAM и оперативными регистрами. Достоинством системы команд можно считать разнообразные режимы адресации ячеек памяти. Как видно из Таблицы 1 (см. группу команд передачи данных), кроме прямой адресации имеются следующие режимы: косвенная, косвенная с пост-инкрементом, косвенная с пре-декрементом и косвенная со смещением.

Поскольку внутренняя и внешняя SRAM входят в единое адресное пространство (вместе с оперативными регистрами и регистрами ввода/вывода), то для доступа к ячейкам внутренней и внешней памяти используются одни и те же команды.

В ячейках оперативной памяти организуется системный стек, который используется автоматически для хранения адресов возврата при выполнении подпрограмм, а также может использоваться программистом для временного хранения содержимого оперативных регистров (команды PUSH и POP). (Микроконтроллеры, не имеющие SRAM, содержат трехуровневый аппаратный стек)

Следует иметь в виду, что если стек располагается во внешней SRAM, то вызовы подпрограмм и возвраты из них требуют двух дополнительных циклов, если бит SRW не установлен, и четырех, если установлен.

Размер стека, организуемого в оперативной памяти, ограничен лишь размерами этой памяти. Если микроконтроллер содержит на кристалле 128 байт внутренней SRAM и не имеет возможности подключения внешней SRAM, то в качестве указателя вершины стека используется регистр ввода/вывода SPL. Если есть возможность подключения внешней памяти или внутренняя память имеет размеры 256 байт и больше, то указатель стека состоит из двух регистров ввода/вывода SPL и SPH.

При занесении числа в стек автоматически выполняются следующие действия:

1. Число записывается в ячейку памяти по адресу, хранящемуся в указателе стека. (SPH:SPL) <- число;

2. Содержимое указателя стека уменьшается на единицу. SPH:SPL = SPH:SPL - 1.

Обратные действия выполняются при извлечении числа из стека:

1. Содержимое указателя увеличивается на единицу. SPH:SPL= SPH:SPL + 1;

2. Число извлекается из ячейки памяти с адресом, хранящимся в указателе стека. (SPH:SPL) -> число.

Таким образом, стек растет от старших адресов к младшим, поэтому учитывая, что начальное значение указателя стека после сброса равно нулю, программист AVR обязательно должен в инициализирующей части программы позаботиться об установке указателя стека, если он предполагает использовать хотя бы одну подпрограмму.

Регистры ввода/вывода, также изображенные на рис. 5, представляют собой набор регистров управления процессорного ядра и регистров управления и данных аппаратных узлов AVR-микроконтроллера. Регистрами ввода/вывода являются упоминавшиеся регистры SREG, MCUSR и указатель стека SPH:SPL а также регистры, управляющие системой прерывания микроконтроллера, режимами подключения EEPROM памяти, сторожевым таймером, портами ввода/вывода и другими периферийными узлами. Изучение данных регистров удобно выполнять одновременно с изучением конкретного периферийного узла.

Все регистры ввода/вывода могут считываться и записываться через оперативные регистры при помощи команд IN, OUT (см. группу команд передачи данных). Регистры ввода/вывода, имеющие адреса в диапазоне $00 - $1F (знак $ указывает на шестнадцатеричную систему счисления), обладают возможностью побитовой адресации. Непосредственная установка и сброс отдельных разрядов этих регистров выполняется командами SBI и CBI (см. группу команд работы с битами). Для признаков результата операции, которые являются битами регистра ввода/вывода SREG, имеется целый набор команд установки и сброса. Команды условных переходов в качестве своих операндов могут иметь как биты-признаки результата операции, так и отдельные разряды побитно адресуемых регистров ввода/вывода.

Регистровый файл, блок регистров ввода/вывода и оперативная память, как показано на рис. 5, образуют единое адресное пространство, что дает возможность при программировании обращаться к 32 оперативным регистрам и к регистрам ввода/вывода как к ячейкам памяти, используя команды доступа к SRAM (в том числе и с косвенной адресацией).

На рис. 5 показано распределение адресов в едином адресном пространстве. Младшие 32 адреса ($0 - $1F) соответствуют оперативным регистрам. Следующие 64 адреса ($20 - $5F) зарезервированы для регистров ввода/вывода. Внутренняя SRAM у всех AVR начинается с адреса $60.

Таким образом, регистры ввода/вывода имеют двойную нумерацию. Если используются команды IN, OUT, SBI, CBI, SBIC, SBIS, то следует использовать нумерацию регистров ввода/вывода, начинающуюся с нуля (назовем ее основной). Если же к регистрам ввода/вывода доступ осуществляется как к ячейкам памяти, то необходимо использовать нумерацию единого адресного пространства оперативной памяти данных AVR. Очевидно, что адрес в едином адресном пространстве памяти данных получается путем прибавления числа $20 к основному адресу регистра ввода/вывода.

Следует отметить, что регистры ввода/вывода не полностью используют отведенные для них 64 адреса. Неиспользуемые адреса зарезервированы для будущих применений, дополнительных ячеек памяти по этим адресам не существует.

Следует также иметь в виду, что у разных типов AVR одни и те же регистры ввода/вывода могут иметь различные адреса. Для того, чтобы обеспечить переносимость программного обеспечения с одного типа кристалла на другой, следует использовать в программе стандартные, принятые в оригинальной фирменной документации, символические имена регистров ввода/вывода, а соответствие этих имен реальным адресам задавать, подключая в начале своей программы (при помощи директивы ассемблера .INCLUDE ) файл определения адресов регистров ввода/вывода.

Файлы определения адресов регистров ввода/вывода имеют расширение .inc . Они уже созданы разработчиками фирмы ATMEL и свободно распространяются вместе с документацией на AVR-микроконтроллеры. В этих файлах задается соответствие символических имен основным адресам регистров ввода/вывода. Если для обращения к регистру ввода/вывода используются команды обмена с SRAM, то к символическому имени необходимо прибавить число $20.

Кроме оперативной памяти программно доступными ресурсами микроконтроллера являются энергонезависимые, электрически программируемые FLASH и EEPROM блоки памяти, которые имеют отдельные адресные пространства.

Так как все команды AVR представляют собой 16-разрядные слова, FLASH-память организована как последовательность 16-разрядных ячеек и имеет емкость от 512 слов до 64K слов в зависимости от типа кристалла.

Во FLASH-память, кроме программы, могут быть записаны постоянные данные, которые не изменяются во время функционирования микропроцессорной системы. Это различные константы, таблицы знакогенераторов, таблицы линеаризации датчиков и т. п. Данные из FLASH памяти могут быть программным образом считаны в регистровый файл при помощи команд LPM, ELPM (см. группу команд передачи данных).

Младшие адреса памяти программ имеют специальное назначение. Адрес $0000 является адресом, с которого начинает выполняться программа после сброса процессора. Начиная со следующего адреса $0001, ячейки памяти программ образуют область векторов прерывания. В этой области для каждого возможного источника прерывания отведен свой адрес, по которому (в случае использования данного прерывания) размещают команду относительного перехода RJMP на подпрограмму обработки прерывания (рис. 5). Следует помнить, что адреса векторов прерывания одних и тех же аппаратных узлов для разных типов AVR могут иметь разное значение. Поэтому для обеспечения переносимости программного обеспечения удобно, так же как и в случае с регистрами ввода/вывода, использовать символические имена адресов векторов прерывания, которые определены в соответствующем inc -файле.

EEPROM блок электрически стираемой памяти данных AVR предназначен для хранения энергонезависимых данных, которые могут изменяться непосредственно на объекте. Это калибровочные коэффициенты, различные уставки, конфигурационные параметры системы и т. п. EEPROM-память данных может быть программным путем как считана, так и записана. Однако специальных команд обращения к EEPROM-памяти нет. Чтение и запись ячеек EEPROM выполняется через регистры ввода/вывода EEAR (регистр адреса), EEDR (регистр данных) и EECR (регистр управления).

ПРИЛОЖЕНИЕ

Таблица 1. Система команд AVR-микроконтроллеров

| Мнемо-код | Операнды | Описание | Операция | Флаги | Кол-во тактов |

| АРИФМЕТИЧЕСКИЕ И ЛОГИЧЕСКИЕ КОМАНДЫ | |||||

| ADD | Rd, Rr | Add without Carry two Registers | Rd Rd + Rr | Z,C,N,V,H | |

| ADC | Rd, Rr | Add with Carry two Registers | Rd Rd + Rr + C | Z,C,N,V,H | |

| ADIW | Rdl, K | Add Immediate to Word | Rdh:Rdl Rdh:Rdl+K | Z,C,N,V,S | |

| SUB | Rd, Rr | Subtract without Carry two Registers | Rd Rd - Rr | Z,C,N,V,H | |

| SUBI | Rd*, K | Subtract Constant from Register | Rd Rd - K | Z,C,N,V,H | |

| SBC | Rd, Rr | Subtract with Carry two Registers | Rd Rd - Rr - C | Z,C,N,V,H | |

| SBCI | Rd*, K | Subtract with Carry Constant from Register | Rd Rd - K - C | Z,C,N,V,H | |

| SBIW | Rdl, K | Subtract Immediate from Word | Rdh:Rdl Rdh:Rdl - K | Z,C,N,V,S | |

| AND | Rd, Rr | Logical AND Registers | Rd Rd · Rr | Z,N,V | |

| ANDI | Rd*, K | Logical AND Register and Constant | Rd Rd · K | Z,N,V | |

| OR | Rd, Rr | Logical OR Registers | Rd Rd v Rr | Z,N,V | |

| ORI | Rd*, K | Logical OR Register and Constant | Rd Rd v K | Z,N,V | |

| EOR | Rd, Rr | Exclusive OR Registers | Rd Rd Å Rr | Z,N,V | |

| COM | Rd | One’s Complement | Rd $FF - Rd | Z,C,N,V | |

| NEG | Rd | Two’s Complement | Rd $00 - Rd | Z,C,N,V,H | |

| SBR | Rd*, K | Set Bit(s) in Register | Rd Rd v K | Z,N,V | |

| CBR | Rd*, K | Clear Bit(s) in Register | Rd Rd · ($FF - K) | Z,N,V | |

| INC | Rd | Increment | Rd Rd + 1 | Z,N,V | |

| DEC | Rd | Decrement | Rd Rd - 1 | Z,N,V | |

| TST | Rd | Test for Zero or Minus | Rd Rd · Rd | Z,N,V | |

| CLR | Rd | Clear Register | Rd Rd Å Rd | Z,N,V | |

| SER | Rd | Set Register | Rd $FF | None | |

| CP | Rd, Rr | Compare | Rd - Rr | Z, N,V,C,H | |

| CPC | Rd, Rr | Compare with Carry | Rd - Rr - C | Z, N,V,C,H | |

| CPI | Rd*, K | Compare Register with Immediate | Rd - K | Z, N,V,C,H | |

| КОМАНДЫ ВЕТВЛЕНИЯ | |||||

| RJMP | k | Relative Jump | PC PC + k + 1 | None | |

| IJMP | Indirect Jump to (Z) | PC Z | None | ||

| JMP | k | Jump | PC k | None | |

| RCALL | k | Relative Subroutine Call | PC PC + k + 1 | None | |

| CALL | k | Call Subroutine | PC k | None | |

| ICALL | Indirect Call to (Z) | PC Z | None | ||

| RET | Subroutine Return | PC STACK | None | ||

| RETI | Interrupt Return | PC STACK | I | ||

| CPSE | Rd,Rr | Compare, Skip if Equal | if (Rd = Rr)PC PC + 2 or 3 | None | 1 / 2 / 3 |

| SBRC | Rr, b | Skip if Bit in Register Cleared | if (Rr(b)=0)PC PC + 2 or 3 | None | 1 / 2 |

| SBRS | Rr, b | Skip if Bit in Register is Set | if (Rr(b)=1)PC PC + 2 or 3 | None | 1 / 2 |

| SBIC | P*, b | Skip if Bit in I/O Register Cleared | if (P(b)=0)PC PC + 2 or 3 | None | 1 / 2 |

| SBIS | P*, b | Skip if Bit in I/O Register is Set | if (P(b)=1)PC PC + 2 or 3 | None | 1 / 2 |

| BRBS | s, k | Branch if Status Flag Set | if (SREG(s) = 1) then PCPC+k + 1 | None | 1 / 2 |

| BRBC | s, k | Branch if Status Flag Cleared | if(SREG(s) = 0) then PCPC+k + 1 | None | 1 / 2 |

| BREQ | k | Branch if Equal | if (Z = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRCS | k | Branch if Carry Set | if (C = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRNE | k | Branch if Not Equal | if (Z = 0) then PC PC + k + 1 | None | 1 / 2 |

| BRCC | k | Branch if Carry Cleared | if (C = 0) then PC PC + k + 1 | None | 1 / 2 |

| BRSH | k | Branch if Same or Higher | if (C = 0) then PC PC + k + 1 | None | 1 / 2 |

| BRLO | k | Branch if Lower | if (C = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRMI | k | Branch if Minus | if (N = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRPL | k | Branch if Plus | if (N = 0) then PC PC + k + 1 | None | 1 / 2 |

| BRGE | k | Branch if Greater or Equal, Signed | if (N Å V= 0) then PC PC + k + 1 | None | 1 / 2 |

| BRLT | k | Branch if Less Than Zero, Signed | if (N Å V= 1) then PC PC + k + 1 | None | 1 / 2 |

| BRHS | k | Branch if Half Carry Flag Set | if (H = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRHC | k | Branch if Half Carry Flag Cleared | if (H = 0) then PC PC + k + 1 | None | |

| BRTS | k | Branch if T Flag Set | if (T = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRTC | k | Branch if T Flag Cleared | if (T = 0) then PC PC + k + 1 | None | 1 / 2 |

| BRVS | k | Branch if Overflow Flag is Set | if (V = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRVC | k | Branch if Overflow Flag is Cleared | if (V = 0) then PC PC + k + 1 | None | 1 / 2 |

| BRIE | k | Branch if Interrupt Enabled | if (I = 1) then PC PC + k + 1 | None | 1 / 2 |

| BRID | k | Branch if Interrupt Disabled | if (I = 0) then PC PC + k + 1 | None | 1 / 2 |

| КОМАНДЫ ПЕРЕДАЧИ ДАННЫХ | |||||

| MOV | Rd, Rr | Move Between Registers | Rd Rr | None | |

| LDI | Rd*, K | Load Immediate | Rd K | None | |

| LD | Rd, X | Load Indirect | Rd (X) | None | |

| LD | Rd, X+ | Load Indirect and Post-Inc. | Rd (X), X X + 1 | None | |

| LD | Rd, - X | Load Indirect and Pre-Dec. | X X - 1, Rd (X) | None | |

| LD | Rd, Y | Load Indirect | Rd (Y) | None | |

| LD | Rd, Y+ | LDLoad Indirect and Post-Inc. | Rd (Y), Y Y + 1 | None | |

| LD | Rd, - Y | Load Indirect and Pre-Dec. | Y Y - 1, Rd (Y) | None | |

| LDD | Rd,Y+q | Load Indirect with Displacement | Rd (Y + q) | None | |

| LD | Rd, Z | Load Indirect | Rd (Z) | None | |

| LD | Rd, Z+ | Load Indirect and Post-Inc. | Rd (Z), Z Z+1 | None | |

| LD | Rd, -Z | Load Indirect and Pre-Dec | Z Z - 1, Rd (Z) | None | |

| LDD | Rd, Z+q | Load Indirect with Displacement | Rd (Z + q) | None | |

| LDS | Rd, k | Load Direct from SRAM | Rd (k) | None | |

| ST | X, Rr | Store Indirect | (X) Rr | None | |

| ST | X+, Rr | Store Indirect and Post-Inc. | ST (X) Rr, X X + 1 | None | |

| ST | - X, Rr | Store Indirect and Pre-Dec. | X X - 1, (X) Rr | None | |

| ST | Y, Rr | Store Indirect | (Y) Rr | None | |

| ST | Y+, Rr | Store Indirect and Post-Inc. | (Y) Rr, Y Y + 1 | None | |

| ST | - Y, Rr | Store Indirect and Pre-Dec. | Y Y - 1, (Y) Rr | None | |

| STD | Y+q,Rr | Store Indirect with Displacement | (Y + q) Rr | None | |

| ST | Z, Rr | Store Indirect | (Z) Rr | None | |

| ST | Z+, Rr | Store Indirect and Post-Inc. | (Z) Rr, Z Z + 1 | None | |

| ST | -Z, Rr | Store Indirect and Pre-Dec | Z Z - 1, (Z) Rr | None | |

| STD | Z+q,Rr | Store Indirect with Displacement | (Z + q) Rr | None | |

| STS | k, Rr | Store Direct to SRAM | (k) Rr | None | |

| LPM | Load Program Memory | R0 (Z) | None | ||

| ELPM | Load Program Memory | R0 (RAMPZ: Z) | None | ||

| IN | Rd, P | In Port | Rd P | None | |

| OUT | P, Rr | Out Port | P Rr | None | |

| PUSH | Rr | Push Register on Stack | STACK Rr; SP SP-1 | None | |

| POP | Rd | Pop Register from Stack | SP SP+1, Rd STACK | None | |

| КОМАНДЫ РАБОТЫ С БИТАМИ | |||||

| SBI | P*,b | Set Bit in I/O Register | I/O(P,b) 1 | None | |

| CBI | P*,b | Clear Bit in I/O Register | I/O(P,b) 0 | None | |

| LSL | Rd | Logical Shift Left | Rd(n+1) Rd(n), Rd(0) 0 | Z,C,N,V | |

| LSR | Rd | Logical Shift Right | Rd(n) Rd(n+1), Rd(7) 0 | Z,C,N,V | |

| ROL | Rd | Rotate Left Through Carry | Rd(0)C,Rd(n+1) Rd(n), CRd(7) | Z,C,N,V | |

| ROR | Rd | Rotate Right Through Carry | Rd(7)C,Rd(n) Rd(n+1),CRd(0) | Z,C,N,V | |

| ASR | Rd | Arithmetic Shift Right | Rd(n) Rd(n+1), n=0..6 | Z,C,N,V | |

| SWAP | Rd | Swap Nibbles | Rd(3..0)Rd(7..4),Rd(7..4)Rd(3..0) | None | |

| BSET | s | Flag Set | SREG(s) 1 SREG(s) | ||

| BCLR | s | Flag Clear | SREG(s) 0 SREG(s) | ||

| BLD | Rd, b | Bit load from T to Register | Rd(b) T | None | |

| BST | Rr, b | Bit Store from Register to T | T Rr(b) | T | |

| SEC | Set Carry | C 1 | C | ||

| CLC | Clear Carry | C 0 | C | ||

| SEN | Set Negative Flag | N 1 | N | ||

| CLN | Clear Negative Flag | N 0 | N | ||

| SEZ | Set Zero Flag | Z 1 | Z | ||

| CLZ | Clear Zero Flag | Z 0 | Z | ||

| SEI | Global Interrupt Enable | I 1 | I | ||

| CLI | Global Interrupt Disable | I 0 | I | ||

| SES | Set Signed Test Flag | S 1 | S | ||

| CLS | Clear Signed Test Flag | S 0 | S | ||

| SEV | Set Twos Complement Overflow | V 1 | V | ||

| CLV | Clear Twos Complement Overflow | V 0 | V | ||

| SET | Set T in SREG | T 1 | T | ||

| CLT | Clear T in SREG | T 0 | T | ||

| SEH | Set Half Carry Flag in SREG | H 1 | H | ||

| CLH | Clear Half Carry Flag in SREG | H 0 | H | ||

| NOP | No Operation | None | |||

| SLEEP | Sleep (see specific description) | None | |||

| WDR | Watchdog Reset | None |

Обозначения, используемые в таблице 1:

Rd - регистр-приемник результата, 0 £ d £ 31

Rd* - регистр-приемник результата, 16 £ d £ 31

Rdl: R24, R26, R28, R30. For ADIW and SBIW instructions

Rr - регистр-источник

P- адрес регистра ввода/вывода

P*- адрес побитно адресуемого регистра ввода/вывода (адреса $00-$1F)

K - символьная или численная константа (8 бит)

k - адресная константа

b - номер бита в регистре (3 бита)

s - номер бита в регистре статуса (3 бита)

X,Y,Z - регистры косвенной адресации (X=R27:R26, Y=R29:R28; Z=R31:R30)

2015-05-20

2015-05-20 1145

1145