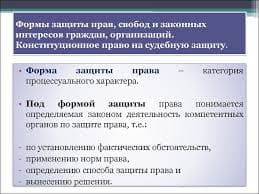

1) Двунаправленный буфер

a) Программируемый для входных и выходных данных;

b) управление двунаправленными операциями на основе использования элементов с тремя состояниями

c) Подтягивающие резисторы (pull-up/pull-down resistors)

d) FFs/Latches используются для улучшения тайминга (время установки – set-up time, время удержания – hold time, задержка распространения от синхровхода до выхода – clock-to-output delay).

2) Routing resources

a) Соединение с центром массива

3) Программируемое I/O напряжение и уровни силы тока

Конфигурируемый блок ввода/вывода используется для организации поступления сигналов к чипу и отправки их во вне. Подтягивающие резисторы используются для подавления сигналов и трактов без необходимости подключения дискретных резисторов вне схемы.

Конфигурируемый блок ввода/вывода используется для организации поступления сигналов к чипу и отправки их во вне. Подтягивающие резисторы используются для подавления сигналов и трактов без необходимости подключения дискретных резисторов вне схемы.

Полярность сигналов на выходах может быть запрограммирована на активно высокий или активно низкий уровень, и зачастую скорость нарастания выходного напряжения на выходе также может быть запрограммирована на быстрое/медленно нарастание и падение. На выходах обычно присутствуют триггеры, так что тактируемые сигналы могут быть выведены напрямую на контакты без значительных задержек (тайминг). Похожим образом триггеры на входах уменьшают задержку сигнала перед достижением триггера.

Программируемые межсоединения (Programmable Interconnect)

Программируемые межсоединения (Programmable Interconnect)

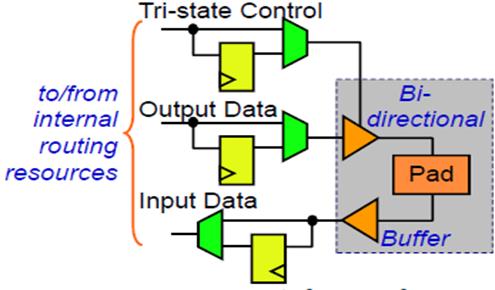

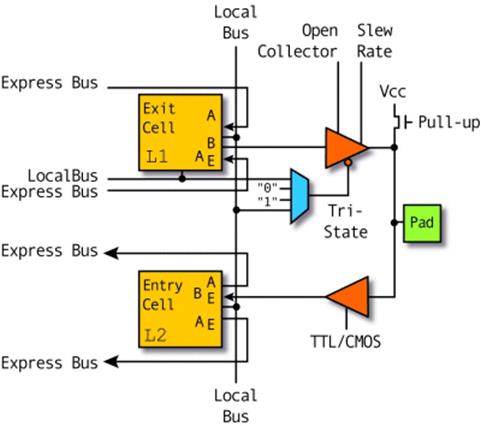

На рисунке 52.12 представлена иерархия межсоединительных ресурсов. Длинные линии используются для соединения критически важных CLBs, которые физически находятся далеко друг от друга на схеме, без значительных задержек. Эти линии также могут быть использованы как шины внутри схемы.

Короткие линии используются для отдельных CLB, расположенных физически близко друг к другу. Транзисторы используются для включения/выключения соединения между различными линиями. Также на программируемой матрице (см. раздел «Программируемые элементы») присутствуют матрицы переключения для соединения этих коротких и длинных линий вместе универсальным образом.

Буферы с тремя устойчивыми состояниями используются для соединения в длинную линию, образующую шину. Специальные длинные линии, называемые общими тактируемыми линиями (global clock lines) спроектированы с низким импедансом и, как следствие, высокой скоростью распространения сигнала. Эти линии соединены с тактируемыми буферами (clock buffers) и с каждым тактируемым элементом в каждом CLB. Таким образом тактируемые сигналы распространяются внутри FPGA с минимальным временными задержками на триггерах внутри схемы.

В FPGA наибольшая задержка на схеме порождается за счет межсоединений, потому что межсоединения, как и логические элементы, строго фиксированы. Для соединения одного CLB блока с другим CLB блоком в разных частях схемы необходимо пройти через большое количество транзисторов и матриц переключения, каждая из которых добавляет задержку.

2015-05-30

2015-05-30 526

526