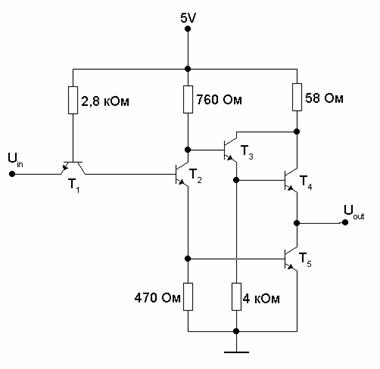

Рис. 33. ТТЛ-схема со сложным инвертором – базовый вариант, реализует логическую функцию И-НЕ

Пусть на один из входов подан U0 – низкий потенциал, тогда соответственно эмиттер МЭТ (Т1) открыт, коллектор МЭТ открыт, потенциал базы транзистора Т2 низкий => Т2 – закрыт (в отсечке); ток эмиттера Т2 – близкий к нулю, потенциал базы Т4 низкий => Т4 – закрыт (в отсечке); потенциал коллектора Т2 (закрытого) – высокий, это потенциал базы Т3, он настолько большой, что открытый эмиттерный переход транзистора Т3 и диод Д, а так как Т4 закрыт, что на выходе высокий потенциал (близкий к Е) – U1.

Пусть на все входы подано высокое напряжение U1 (близкое к Е), тогда все эмиттерные переходы МЭТа Т1 закрыты, коллекторный переход открыт и ток через него течет в базу транзистора Т2, Т2 – в режиме насыщения Т4 – также в режиме насыщения:

UK1 – UK2 = UD_ОТКР + UКЭ_НАС - UКЭ_НАС < 2UD_ОТКР, следовательно, эмиттерный переход Т3 и диод D отрыться не могут, значит они в отсечке.

На выходе: UВЫХ=UКЭ_НАС=50мВ=U0, т.о. выполняется таблица истинности функции И‑НЕ: U1»E, U0=UКЭ_НАС»50 мB.

Чаще всего по входу и выходу логической схемы подключены такие же логические схемы, чтобы выполнять сложную логическую функцию, следовательно, сигналы на входе и выходе схемы одинаковы.

а) б)

Рис. 34.

а) вольт-амперная характеристика p-n – перехода,

б) передаточная характеристика ТТЛ-схема со сложным инвертором

Когда UВХ = 0, Т2 закрыт и на выходе напряжение равно:

UВЫХ = U1 = E ‑ 2U*, напряжение питания минус падение напряжения на открытых p-n – переходах: эмиттера T3 и диода.

Пока входное напряжение не станет равным: UВХ = U0П ПР =UЭЗ – UКЭН, Т2 закрыт и на выходе напряжение не меняется (UВЫХ =U1), после этого момента Т2 переходит в нормальный активный режим, за счет тока IЭ2 создается падение напряжения на R4 и напряжение UБ4 увеличивается, так как Т2 в нормальном активном режиме, через R2 течет ток, уменьшается UК2 и вслед за ним UВЫХ:

UВХ=U0П = U* + UЭЗ – UКЭН,

когда напряжение на базе Т4 достигает UБ4=UЭЗ и Т4 открывается, переходя в нормальный активный режим, и UВЫХ начинает резко падать, начиная со значения:

U1ПР = U1 ‑ DU1ВЫХ = E ‑ 2U* ‑ UЭЗR2/R4,

Когда UВХ=U1П = 2U* – UКЭН, оба транзистора в насыщении и на выходе: UВЫХ =U0=UКЭН.

Рассматриваемая схема является наиболее распространенной схемой логической ТТЛ ячейки, проектирование которой рассмотрено в книге [5, глава 2]. В указанной книге приводится методика расчета и численый пример.

Топологию ТТЛ схемы рассмотрим на примере логической схемы НЕ (инвертора) со схемой Дарлингтона (составным транзистором) в выходной цепи.

Рис. 35. ТТЛ инвертор

Рис. 36. Топология ТТЛ инвертора

КМОП

В схемах данного типа используются как n-канальные, так и p-канальные МДП транзисторы. Это позволяет создать логические схемы, практически не потребляющие мощность в статическом режиме. У таких схем потребляемая мощность на низких и средних частотах на 2-3 порядка меньше, чем у ТТЛ схем, а задержка примерно такая же. Эти схемы применяются при наличии ограничений на потребляемую мощность из-за ограниченных энергоресурсов или жестких требований к тепловому режиму. Однако они технологически сложнее и занимают большую площадь на кристалле.

2015-06-05

2015-06-05 2235

2235