2.1. Центральный процессор вычислительной машины, управляемый микропрограммой.

Один из многих параметров, характеризующих ВС, рабочий цикл процессора иначе называется циклом центрального процессора либо машинным циклом. Это время, требуемое для выборки из памяти и выполнения одной простой машинной команды, например, сложения и вычитания.

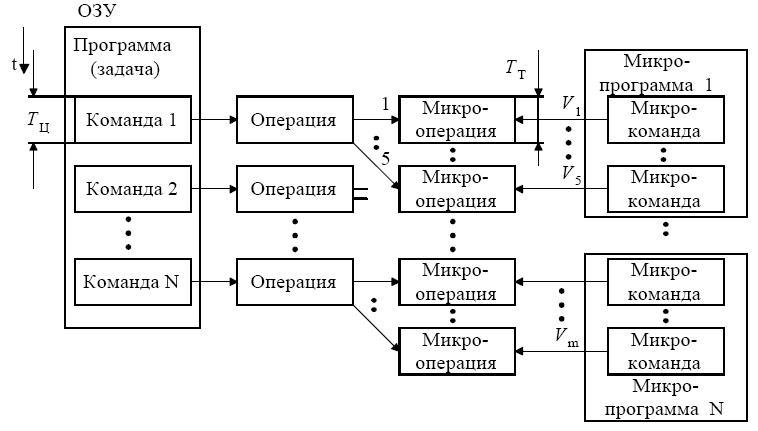

Рисунок 2.1.1. Распределение во времени выполнения команд и микрокоманд

На рисунке 2.1.1. это время обозначено Tц. По команде программы в АЛУ центрального процессора выполняются арифметические и логические действия над операндами, который называются операциями. Выполнение операции производится по частям, называемым микрооперациями - элементарным операциям, выполняемым за один машинный такт ТТ. Таким образом, каждой микрооперации соответствует выполняемое в АЛУ элементарное действие передачи информации между регистрами общего назначения РОН или ее преобразования. Это действие инициируется (вызывается) поступлением управляющего сигнала V на внутреннюю управляющую шину. Для реализации команды необходимо на соответствующие линии ШУ подать распределенную во времени последовательность управляющих сигналов Vi, Vi+ 1, Vi +2,... Их вырабатывает управляющий блок УУ. Последовательность микрокоманд, необходимых для выполнения операции, называется микропрограммой. Микропрограммная интерпретация микрокоманд иллюстрируется на рисунке 2.1.2.

|

|

|

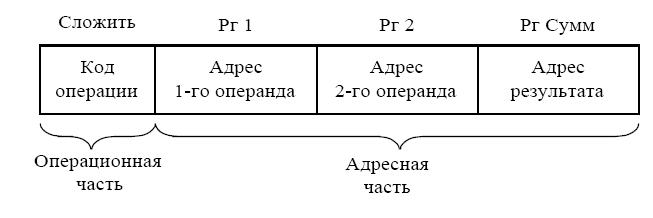

Рисунок 2.1.2. –структурное представление трехадресной команды.

Таким образом, УУ вырабатывает управляющие сигналы для осуществления выборки кода очередной команды из памяти, дешифрации кода команды, нормирования адресов операндов, выборки операндов из памяти, передачи их в АЛУ, выполнения в АЛУ операции, предусмотренной кодом команды, передачи результата в память. Последовательности управляющих сигналов V вызывают выполнение в процессоре микроопераций. В процессорах малых и средних ЭВМ часто применяют микропрограммное УУ. В больших же машинах применяется управление с «жесткой» логикой, то есть аппаратно реализованной, что приводит к повышению быстродействия ЭВМ. В МП наборах разных типов применяются оба способа выработки управляющих сигналов.

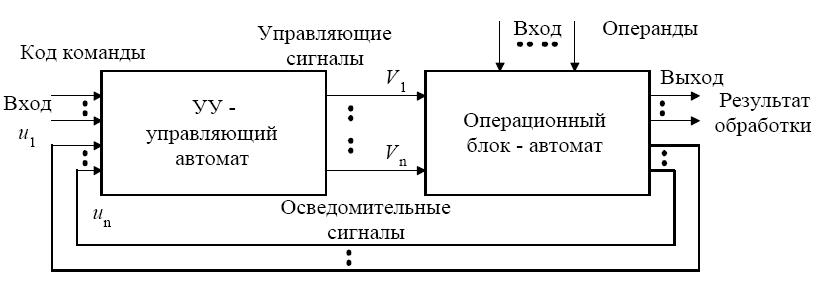

УУ можно рассматривать как конечный автомат (рис. 2.1.3.), определяемый:

1. Множеством входных сигналов (u1, u2,...,un), соответствующих задаваемому УУ извне двоичному коду операции (КОП) и двоичным значениям осведомительных сигналов.

2. Множеством двоичных выходных сигналов (V 1, V 2,... V m), соответствующих множеству микроопераций операционного блока - АЛУ. При V i =1 возбуждается i-я микрооперация.

3. Множеством подлежащих реализации микропрограмм, устанавливающих в зависимости от значении входных сигналов ui управляющие сигналы, выдаваемые устройством управления в определенные такты.

|

|

|

Рисунок 2.1.3. Условное представление процессора как два конечных автомата.814

По множествам входных и выходных сигналов и микропрограмм определяется множество внутренних состояний УУ (Q0, Q1, Q2,...Qr).

Управляющий автомат может быть задан, как автомат Мура:

Q(t+1)=A[Q(t), u1(t), u2(t),...,un(t)];

V 1(t)=B1[Q(t)];

........................

V m(t)=Bm[Q(t)];

или как автомат Мили (автомат с памятью)

Q(t+1)=A[Q(t), u1(t), u2(t),...,un(t)];

V 1(t)=B1[Q(t), u1(t), u2(t),...,un(t)];

........................

V m(t)=Bm[Q(t), u1(t), u2(t),...,un(t)],

где функции переходов и выходов А, В определяются выданной из памяти микропрограммой.

Автомат находится в состоянии Q(t) в течение времени ТTi, а в состоянии Q(t+1) – в следующем такте ТTi+ 1.

Операционный блок - АЛУ – тоже является конечным автоматом. Взаимодействие двух конечных автоматов. Процессор строится на 2-х разнотипных автоматах, Мура и Мили.

2015-08-21

2015-08-21 2555

2555