У даній обчислювальній системі використовується введення-виведення інформації з відображенням у пам‘ять. Такий спосіб введення-виведення інформації передбачає, що ПВВ та ОП використовують спільний адресний простір. Це означає, що структурні вузли кожного ПВВ (регістр стану (PC) та регістр даних (РД)) мають свої адреси, включені в загальний адресний простір обчислювальної системи, й звертання до них здійснюється як до комірок пам‘яті.

Крім РС та РД (рис. 19) до складу ПВВ входить тригер запиту переривання, який не є адресованим вузлом. Тригер дає сигнал IRQ (Interrupt ReQuest – запит на переривання), нульовий рівень якого свідчить про те, що ПВВ потребує зв‘язку з процесором для виведення слова з процесора (акумулятора (А)) або введення слова в акумулятор процесора, функції якого виконує R15 АЛП.

Крім РС та РД (рис. 19) до складу ПВВ входить тригер запиту переривання, який не є адресованим вузлом. Тригер дає сигнал IRQ (Interrupt ReQuest – запит на переривання), нульовий рівень якого свідчить про те, що ПВВ потребує зв‘язку з процесором для виведення слова з процесора (акумулятора (А)) або введення слова в акумулятор процесора, функції якого виконує R15 АЛП.

У системі передбачено вісім ПВВ, в конкретний момент часу можлива робота лише з одним ПВВ.

ПВВ виконує дві мікрооперації:

·  введення інформації в акумулятор процесора з вибраного ПВВ (ініціюється сигналом I (Input), який мнемонічно позначатиме { i; }),

введення інформації в акумулятор процесора з вибраного ПВВ (ініціюється сигналом I (Input), який мнемонічно позначатиме { i; }),

|

|

|

·  виведення інформації з акумулятора у вибраний ПВВ (ініціюється сигналом O (Output), який мнемонічно позначатимемо { o; }).

виведення інформації з акумулятора у вибраний ПВВ (ініціюється сигналом O (Output), який мнемонічно позначатимемо { o; }).

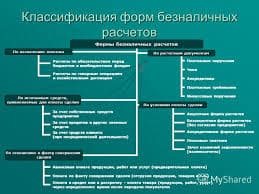

Обмін інформацією між акумулятором процесора та ПВВ здійснюється через регістр даних зовнішнього пристрою. Але звертання до РД можливе тільки в тому випадку, якщо в РС встановлено біт готовності до обміну (рис. 20). Це означає, що перед звертанням до РД необхідно перевірити біт готовності в РС. Звертання до РС можливе в будь-який момент часу.

2015-08-21

2015-08-21 317

317