Сдвиговые регистры. Схема таблицы истинности. Графики

Регистры. Общее понятие. Параллельная запись в регистры. Таблица истинности.

Синхронный jk-триггер. Таблица истинности. Режим работы. Графики.

Синхронный D-триггер. Таблица истинности. Режим работы. Графики.

D-триггер. или триггер задержки (от английского delay-задержка), при разрешающем сигнале на тактовом входе устанавливается в состояние, соответствующее потенциалу на входе D. Если обозначать выходной сигнал триггера буквой Q, то для D-тригтера можно написать следующее равенство: Qn=Dn-1. Индексы n и n-1 указывают на то, что выходной сигнал Q изменяется не сразу после изменения входного сигнала D, а только с приходом разрешающего тактового сигнала. Тактирование D-триггера может о существляться импульсом или фронтом. В тактируемом фронтом D-триггере изменение потенциала на входе D, синхронное с тактовыми импульсами, повторяется на выходе Q с задержкой на один период тактовых импульсов (отсюда и название-триггер задержки). На рисунке 1 показаны: структурная схема, условное обозначение и временная диаграмма D-триггера.

|

|

|

|

|

|

| ||||||

| а. | б. в. | г. |

Рис. 1. D-триггер:

а- таблица истинности б - структурная схема; в - условное обозначение г - временные диаграммы

Он состоит из синхронного RS-триггера и инвертора. Благодаря инвертору невозможно запрещенное соотношение сигналов на входах S и R. Из временной диаграммы (рис. 1в) видно, что D-триггер осуществляет задержку установки Q на время, отделяющее момент из менения сигнала D от начала очередного тактового импульса, причем выходной сигнал Q сохраняется до прихода очередного тактового импульса.

Прежде чем начать изучение JK-триггера, вспомним принципы работы RS-триггера. Напомню, что в этом триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы R и S запрещены. Очень хотелось бы избавиться от этой неприятной ситуации.

Таблица истинности JK-триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц JK-триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов JK-триггер изменяет своё состояние на противоположное. Таблица истинности JK-триггера приведена в таблице 1.

Таблица 1. Таблица истинности JK-триггера.

| С | K | J | Q(t) | Q(t+1) | Пояснения |

| x | x | Режим хранения информации | |||

| x | x | ||||

| Режим хранения информации | |||||

| Режим установки единицы J=1 | |||||

| Режим записи нуля K=1 | |||||

| K=J=1 счетный режим триггера | |||||

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1.

|

|

|

Рисунок 1. Внутренняя схема JK-триггера.

Для реализации счетного режима в схеме, приведенной на рисунке 8.22, введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря этой обратной связи на входах R и S никогда не может возникнуть запрещенная комбинация.

Приводить временные диаграммы работы JK-триггера не имеет смысла, так как они совпадают с приведёнными ранее диаграммами RS- и T-триггера. Условно-графическое обозначение JK-триггера приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение JK-триггера.

На этом рисунке приведено обозначение типовой цифровой микросхемы JK-триггера, выполненной по ТТЛ технологии. В промышленно выпускающихся микросхемах обычно кроме входов JK-триггера реализуются входы RS-триггера, которые позволяют устанавливать триггер в заранее определённое исходное состояние.

В названиях отечественных микросхем для обозначения JK-триггера присутствуют буквы ТВ. Например, микросхема К1554ТВ9 содержит в одном корпусе два JK-триггера. В качестве примеров иностранных микросхем, содержащих JK-триггеры можно назвать такие микросхемы, как 74HCT73 или 74ACT109.

Так как JK-триггер является универсальной схемой, то рассмотрим несколько примеров использования этого триггера. Начнем с примера использования JKтриггера в качестве обнаружителя коротких импульсов.

Рисунок 3. Схема обнаружения короткого импульса.

В данной схеме при поступлении на вход “C” импульса триггер переходит в единичное состояние, которое затем может быть обнаружено последующей схемой (например, микропроцессором). Для того, чтобы привести схему в исходное состояние, необходимо подать на вход R уровень логического нуля.

Теперь рассмотрим пример построения на JK-триггере ждущего мультивибратора. Один из вариантов подобной схемы приведен на рисунке 4.

Рисунок 4. Схема ждущего мультивибратора.

Схема работает подобно предыдущей схеме. Длительность выходного импульса определяется постоянной времени RC цепочки. Диод VD1 предназначен для быстрого восстановления исходного состояния схемы (разряда емкости C). Если быстрое восстановление схемы не требуется, например, когда длительность выходных импульсов гарантированно меньше половины периода следования входных импульсов, то диод VD1 можно исключить из схемы ждущего мультивибратора.

В качестве последнего примера применения универсального JK-триггера, рассмотрим схему счетного T-триггера. Схема счетного триггера приведена на рисунке 5.

В схеме, приведенной на рисунке 5, для реализации счетного режима работы триггера на входы J и K подаются уровни логической единицы

Регистры (англ. register) представляют собой, по сути, несколько D-триггеров (обычно от 4 до 16), соединенных между собой тем или иным способом. Поэтому принципиальной разницы между ними и отдельными D-триггерами не существует. Правда, триггеры, входящие в состав регистров, не имеют такого количества разнообразных управляющих входов, как одиночные триггеры.

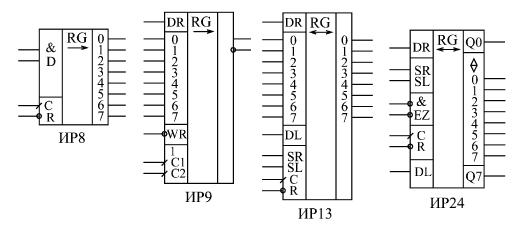

На схемах регистры обозначаются буквами RG. В отечественных сериях микросхем регистрам соответствуют буквы ИР. Все регистры делятся на две большие группы (рис. 8.1):

- Параллельные регистры;

- Регистры сдвига (или сдвиговые регистры).

Существуют регистры и других типов, но они применяются гораздо реже, чем параллельные и сдвиговые, так как имеют узкоспециальное назначение.

|

|

|

В параллельных регистрах (а) каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый информационный выход. Тактовые входы (С) всех триггеров соединены между собой. В результате параллельный регистр представляет собой многоразрядный, многовходовый триггер.

Рис. 8.1. Структура параллельного регистра (а)и сдвигового регистра (б)

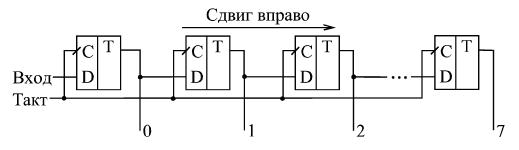

В сдвиговых регистрах (б) все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться - в зависимости от функции, выполняемой регистром.

Параллельные регистры, в свою очередь, делятся на две группы:

- Регистры, срабатывающие по фронту управляющего сигнала С (или тактируемые регистры).

- Регистры, срабатывающие по уровню управляющего сигнала С (или стробируемые регистры).

Чаще всего в цифровых схемах используются регистры, управляемые фронтом (то есть тактируемые), однако и стробируемые регистры имеют свой круг задач, в которых их ничто не может заменить.

Таблица 3 – Таблица истинности регистра сдвига К555ИР10

| Режим работы | Вход | Выход | Внутр. | ||||

| EL | C | R | D0-D7 | D8 | q1-q8 | ||

| загрузка | н | | в | x | н | н | x |

| н | | в | x | в | В | x | |

| сдвиг | в | | в | x | х | Q7 | x |

| хранение | в | в | в | x | x | q | x |

| в | н | в | x | x | q | x | |

| сброс | x | x | н | x | x | н | н |

Регистры сдвига или сдвиговые регистры (англ. shift register) представляют собой, как уже отмечалось, последовательно соединенную цепочку триггеров. Основной режим их работы – это сдвиг разрядов кода, записанного в эти триггеры, То есть по тактовому сигналу содержимое каждого предыдущего триггера переписывается в следующий по порядку в цепочке триггер. Код, хранящийся в регистре, с каждым тактом сдвигается на один разряд в сторону старших разрядов или в сторону младших разрядов, что и дало название регистрам данного типа.

|

|

|

В связи с названием направления сдвига в сдвиговых регистрах часто возникает путаница. Сдвиг бывает двух видов: вправо (основной режим, который есть у всех сдвиговых регистров) и влево (этот режим есть только у некоторых, реверсивных сдвиговых регистров). Названия эти отражают внутреннюю структуру регистров сдвига (рис. 8.14) и перезапись сигналов последовательно по цепочке триггеров. При этом триггеры, вполне естественно, нумеруются слева направо, например, от 0 до 7 (или от 1 до  для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево – это сдвиг в сторону разрядов, имеющих меньшие номера.

для 8-разрядных регистров. В результате сдвиг информации регистром вправо представляет собой сдвиг в сторону разрядов, имеющих большие номера, а сдвиг информации регистром влево – это сдвиг в сторону разрядов, имеющих меньшие номера.

Однако, как известно, в любом двоичном числе слева расположены старшие разряды, а справа – старшие разряды. Поэтому сдвиг двоичного числа вправо будет сдвигом в сторону младших разрядов, а сдвиг влево – сдвигом в сторону старших разрядов. Это противоречие, не чей-то злой умысел, просто так исторически сложилось, и об этом надо помнить разработчику цифровой аппаратуры.

Рис. 8.14. Направление сдвига в сдвиговых регистрах

В стандартные серии цифровых микросхем входит несколько типов сдвиговых регистров, отличающихся возможными режимами работы, режимами записи, чтения и сдвига, а также типом выходных каскадов (2С или 3С). Большинство регистров сдвига имеет восемь разрядов. На рис. 8.15 представлены для примера четыре типа микросхем регистров сдвига.

Регистр ИР8 – наиболее простой из регистров сдвига. Он представляет собой 8-разрядную линию задержки, то есть имеет только один информационный вход, на который подается последовательная сдвигаемая информация (точнее, два входа, объединенных по функции 2И), и восемь параллельных выходов. Сдвиг в сторону выходов со старшими номерами осуществляется по переднему фронту тактового сигнала С. Имеется также вход сброса –R, по нулевому сигналу на котором все выходы регистра сбрасываются в нуль. Таблица истинности регистра ИР8 приведена в табл. 8.5.

Рис. 8.15. Сдвиговые регистры

Таблица 8.5. Таблица истинности регистра сдвига ИР8

| Входы | Выходы | ||||||

| -R | C | D1 | D2 | Q0 | Q1 | … | Q7 |

| X | X | X | … | ||||

| X | X | Не меняются | |||||

| Х | Х | Не меняются | |||||

| Q0 | … | Q6 | |||||

| Х | Q0 | … | Q6 | ||||

| Х | Q0 | … | Q6 |

Арифметико-логическое устройство процессора (АЛУ) обязательно содержит в своем составе такие элементы как сумматоры. Эти схемы позволяют складывать двоичные числа.

Как происходит сложение? Допустим, требуется сложить двоичные числа 1001 и 0011. Сначала складываем младшие разряды (последние цифры): 1+1=10. Т.е. в младшем разряде будет 0, а единица – это перенос в старший разряд. Далее: 0 + 1 + 1(от переноса) = 10, т.е. в данном разряде снова запишется 0, а единица уйдет в старший разряд. На третьем шаге: 0 + 0 + 1(от переноса) = 1. В итоге сумма равна 1100.

2013-12-29

2013-12-29 726

726