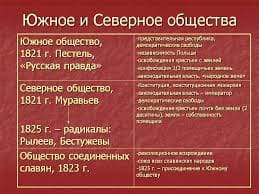

Накопитель организован на 16 микросхемах ФЛЭШ-памяти K9K49G08U0M, которые разделим на четыре банка, по четыре микросхемы в каждом банке (рисунок 3.7). Это сделано для того чтобы иметь возможность устранить времена простоя (занятости) накопителя при циклах записи. Все 16 микросхем имеют общую шину данных, сигналы записи, чтения, записи команд и адреса. Выборка между микросхемами осуществляется сигналом Выбора микросхемы (СЕ). Сигналы R/B (свободен/занят) микросхем, объединенных в банк, соединены, следовательно для анализа контроллеру доступно четыре сигнала свободен/занят (R/B) определяющие занятость банков.

Рисунок 3.7 – Структура накопителя

Такое построение накопителя с одной стороны позволяет производить непрерывную запись в него, а с другой стороны оптимизирует число линий связи необходимое для его обслуживания.

Быстрая промежуточная память

Скоростная буферная память организована на микросхеме быстродействующего ОЗУ IDT71V424S15YI. Она имеет организацию 512к×8, и позволяет производить запись с периодом 15 нс. Микросхема всеми сигнальными выводами подключена к ПЛИС, так как имеет связи только с ее внутренними узлами.

Исходные данные на проектирование разрабатываемой системы

При разработке конструкции необходимо применить многослойный стеклотекстолит. Габаритные размеры, места креплений, расположение разъёмов ESQT аналогично ячейке АЦП-079-03. Контакты всех разъёмов не должны измениться. Фильтрующие конденсаторы располагать вблизи выводов микросхем потребителей. В схеме применена программируемая логическая матрица фирмы ALTERA.

Выводы элемента IDT71V424S пригодные для перестановки приведены в таблице 3.3. Выводы разделены на две независимые группы. Данная перестановка применима только для этого проекта.

Таблица 3.3 – Выводы элемента IDT71V424S

| Группа | Название | Вывод | Группа | Название | Вывод |

| 1 | A0 | 1 | 1 | A14 | 24 |

| 1 | A1 | 2 | 1 | A15 | 32 |

| 1 | A2 | 3 | 1 | A16 | 33 |

| 1 | A3 | 4 | 1 | A17 | 34 |

| 1 | A4 | 5 | 1 | A18 | 35 |

| 1 | A5 | 14 | 2 | D0 | 7 |

| 1 | A6 | 15 | 2 | D1 | 8 |

| 1 | A7 | 16 | 2 | D2 | 11 |

| 1 | A8 | 17 | 2 | D3 | 12 |

| 1 | A9 | 18 | 2 | D4 | 25 |

| 1 | A10 | 20 | 2 | D5 | 26 |

| 1 | A11 | 21 | 2 | D6 | 29 |

| 1 | A12 | 22 | 2 | D7 | 30 |

| 1 | A13 | 23 |

Данная система регистрации данных должна обеспечивать 2 варианта подключения:

– первый вариант в составе ИВК-079-03;

– второй вариант в составе независимого блока БСИ совместно с ячейкой БСИ-2.

Разъёмы Х3, Х4 расположить на краю ячейки. Расположение элементов необходимо согласовать с отделом 210.

2020-01-14

2020-01-14 285

285