Архитектура микропроцессора

Тема 1

Микропроцессор (МП) по своим функциям эквивалентен процессору ЭВМ. Это программно-управляемое устройство, осуществляющее процесс обработки информации и управление им, построенное на одной большой интегральной схеме (БИС). В настоящее время в мире выпускается более ста типов микропроцессоров. Такое разнообразие МП определяется различным сочетанием их характеристик, однако, любой из них предназначен для выполнения последовательных команд, предусмотренных программой. Большое распространение получил микропроцессорный комплект БИС серии КР580, предназначенный для создания широкого класса средств вычислительной техники и обработки информации. На основе комплекта строятся микроЭВМ контрольно-измерительных систем, микроЭВМ для управления технологическими процессами, контроллеры периферийных устройств, бытовых приборов и игровых автоматов. МПК КР580 выполнен по n-МОП технологии и напряжения логических уровней согласуется с ИС ТТЛ. Кроме того, МП КР580 имеет архитектуру, по которой разрабатываются более современные и производительные микропроцессоры. Под архитектурой МП понимают его логическую организацию, определяемую возможностями микропроцессора по аппаратной или программной реализации функций, необходимых для осуществления процесса обработки информации.

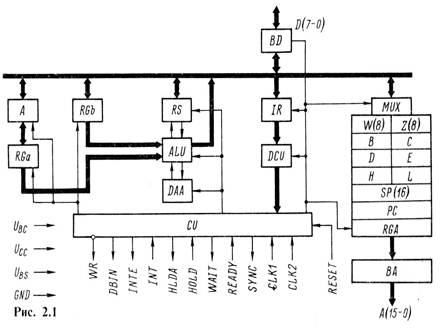

Структурная схема микропроцессора приведена на рис. 1.1. В состав БИС входят: 8-разрядное арифметико-логическое устройство (ALU)', регистр признаков (RS), фиксирующий признаки, вырабатываемые ALU в процессе выполнения команд; аккумулятор (А)', регистр аккумулятора (RGa), регистр временного хранения операндов (RGb)-, десятичный корректор (DAA), выполняющий перевод информации из двоичной в двоично-десятичную форму; регистр команд (IR), предназначенный для хранения первого байта команды, содержащего код операции; дешифратор команд (DCU), блок регистров для приема, выдачи и хранения информации в процессе выполнения программ, содержащий программный счетчик (PC), указатель стека (SP), регистр адреса (PGA), шесть регистров общего назначения (В, С, D, Е, Н, L) и вспомогательные регистры (Wn Z); схема управления и синхронизации (CU), формирующая последовательность управляющих сигналов для работы ALU и блока регистров; 16-разрядный буферный регистр адреса (ВА)-, 8-разрядный буферный регистр данных (BD), двунаправленный мультиплексор (MU X) для обме

на операндами и результатами операций между ALU и блоком регистров по внутренней шине данных.

Рис. 1.1.

Рис. 1.1.

Программный счетчик предназначен для хранения текущего адреса команды, автоматически увеличивающегося в процессе выполнения команды на 1, 2 или 3 в зависимости от формата выполняемой команды.

Указатель стека содержит адрес вершины стека, а сам стек может использовать любую зону оперативного запоминающего устройства (ОЗУ) объемом до 64К байт или специальное ЗУ, адресуемое сигналом STACK. Содержимое указателя стека уменьшается на 2, когда данные загружаются в стек, и увеличивается на 2, когда данные извлекаются из стека.

Микропроцессор имеет 16-разрядный трехстабильный канал адреса А(15-0), 8-разрядный двунаправленный трехстабильный канал данных D (7-0), четыре входных и шесть выходных выводов управления. МП обеспечивает адресацию внешней памяти объемом до 64К байт, а также адресацию 256 устройств ввода и 256 устройств вывода.

Назначения входных, выходных и управляющих сигналов МП приведены при описании выводов микросхемы в табл. 1.1.

Таблица 1.1. Описание выводов микросхемы

| Обозначения выводов | Номера контактов | Назначение выводов |

| А(15 - 0) | 25; 26; 27; 29; 30; 31; 32; 33; 34; 35; 1; 40; 37; 38; 39; 36 | Трехстабильная 16-разрядная шина адреса |

| D(7-0) | 10: 9; 8; 7; 3; 4; 5; 6 | Двунаправленная трехстабильная 8-разрядная шина данных |

| WR | Выход сигнала «выдача» - напряжение L-уровня указывает на выдачу байта информации на шину D(7-0) для записи в ЗУ или устройство ввода-вывода (УВВ) | |

| DBIN | Выход сигнала «прием» - напряжение Н-уровня указывает на прием с шины D(7 - 0) байта информации, выданного ЗУ или УВВ | |

| INTE | Выход сигнала «разрешение прерывания» | |

| INT | Вход сигнала «запрос на прерывание» | |

| HLDA | Выход сигнала «подтверждение захвата» - напряжение H-уровня указывает на перевод шин адреса и данных МП в высокоимпедансное состояние | |

| HOLD | Вход сигнала «захват» - напряжение H-уровня указывает на запрос другими устройствами системы на управление шинами системы | |

| WAIT | Выход сигнала «ожидание» - напряжение H-уровня указывает на состояние ожидания МП | |

| READY | Вход сигнала «готовность» - напряжение H-уровня указывает на готовность данных на шине D(7 -0) к вводу в МП или на готовность внешних устройств к приему информации, служит для синхронизации микропроцессора с ЗУ или УВВ | |

| SYNC | Выход сигнала «синхро» - напряжение H-уровня идентифицирует начало каждого машинного цикла | |

| CLKI | Вход фазы 1 | |

| CLK2 | Вход фазы 2 | |

| RESET | Вход установки 0 - установка счетчика команд в нуль, сброс триггеров разрешения прерывания и захвата шин | |

| ubc | Напряжение питания (+12 В) | |

| Ucc | Напряжение питания (+5 В) | |

| ubs | Напряжение питания (-5 В) | |

| GND | Напряжение питания (0 В) | |

| Примечание: L-уровень- низкий логический уровень: H-уровень - высокий логический уровень |

2014-02-24

2014-02-24 2162

2162