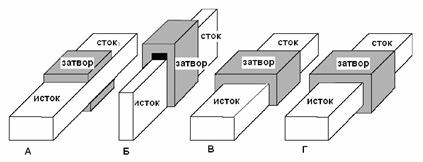

Технология КНИ является естественным шагом для перехода от чисто планарного принципа интеграции к объемной (3D) интеграции. Одна из главных целей объемной интеграции – подавление геометрических короткоканальных эффектов –реализуется в технологиях многозатворных МОПТ. На рис. 6.10 изображены несколько перспективных многозатворных конфигураций МОПТ.

|

Рис. 6.10. Структуры КНИ многозатворных (multiple gate) транзисторов: (А) планарный транзистор с двойным затвором (double-gate −DG); (Б) FinFET; (В) тройной (П-затвор); (Г) круговой затвор

Особенностью таких структур является высокое электростатическое качество и высокая степень управляемости зарядом в канале. Идеальным в этом смысле является транзистор с круговым затвором, он же является наиболее сложным технологически. Транзисторы с тройным (П-образным или Ω-образным) затвором и так называемый FinFET (от английского слова fin – рыбий плавник) вполне совместимы с уже существующей технологией изготовления и уже реализованы в 32 и 22 нм технологии Intel.

Транзистор с горизонтальным двойным затвором (DG) является самым перспективным в смысле компромисса между электростатическим качеством, а также степенью интеграции и сложностью изготовления. В нем может реализовываться не только режим работы с двумя каналами, но и режим объемной инверсии. У него больше ток, подпороговый размах близок к 60мВ/декаду, носители, текущие в середине пленки, испытывают меньшее рассеяние. Поэтому подвижность и радиационная стойкость улучшаются, а низкочастотный шум уменьшается. Короткоканальные эффекты (DIBL, DIVSB, прокол) сокращаются, следовательно, минимальная длина канала у DG транзисторов меньше, чем у однозатворных (SG −single gate) приборов. Численное моделирование, включающее квантоворазмерные эффекты, туннелирование зона-зона и прямое туннелирование исток-сток, дает приемлемые характеристики даже для DG транзисторов с длиной канала 2…8 нм. При этом рекомендуемое отношение толщины пленки к длине канала для DG транзисторов составляет 1/2, в противоположность SG транзисторам (1/4). DG транзистор реализуется на основе традиционной планарной технологии, однако существуют значительные трудности с совмещением верхнего и нижнего затворов.

Зададимся вопросом: всякие ли альтернативные структуры к планарным объемным структурам МОПТ могут использоваться для масштабирования КМОПТ в суб-10нм область длин затвора? Чтобы ответить на этот вопрос, полезно рассмотреть требования (перечисленные в порядке их важности), предъявляемые к «совершенному» МОПТ:

1. Невосприимчивость к случайным флуктуациям примеси (random dopant fluctuation, RDF).

2. Электростатическое качество выше, чем у планарных объемных МОПТ.

3. Относительная простота изготовления.

4. Возможность динамической регулировки порогового напряжения.

5. Эффективность топологического размещения элементов такая же или лучше, чем у планарных объемных МОПТ.

Для удовлетворении первого требования концентрация примеси в канале должна быть низкой. Для выполнении второго требования необходимы многозатворные транзисторы. Для реализации третьего требования необходимо избегать суб-5нм толщины канала или высокого аспектового отношения топологических элементов (например, «плавников» с отношением высоты к ширине больше 3). Чтобы исполнить четвертое требование, необходим нижний затвор (ВG MOSFET) или непосредственный контакт к базе. Хотя пятое требование не является критическим, оно благоприятствует транзисторным структурам, которые обеспечивают бòльшую ширину канала на шаг металлизации. Из всех транзисторов с тонкой базой только планарные ВG MOSFET (с соответствующим смещением нижнего затвора) могут удовлетворить всем этим требованиям. Практическое изготовление ВG MOSFET определяется стоимостью КНИ подложек с очень тонким (<10нм) и однородным скрытым слоем.

Другой путь продолжения масштабирования КМОПТ заключается в эволюции традиционного планарного объемного МОПТ в многозатворную структуру − трехзатворный объемный МОПТ (TG bulk MOSFET). Этого можно достигнуть сегментированием области канала на параллельные полоски равной ширины и «обертывания» электрода затвора вокруг верхней части каждой полоски, как показано на рис. 6.11.

|

На практике такая рифленая структура затвора может быть достигнута путем создания канавок в изоляции в промежутках между полосками до формирования затвора, как это делается при создании FinFET. Для подавления подпороговых утечек и ослабления вариации порогового напряжения вследствие RDF должно использоваться суперступенчатое ретроградное легирование, локализованное в базе под полосками затвора. Так как затвор окружает канал, величина заряда ОПЗ под затвором на единицу ширины канала меньше, чем в планарном приборе, так что вариации порогового напряжения вследствие RDF уменьшаются.

Использование TG bulk MOSFET позволяет достичь более высокого электростатического качества, чем у TG SOI MOSFET, так как исключается проникновение электрического поля сквозь скрытый окисел.

Важно заметить, что изготовление TG bulk MOSFET обеспечивает более низкое паразитное сопротивление стока и истока ( ), чем у MOSFET с тонкой базой, так как не требуется ни ультратонкая (UTB) пленка кремния, ни очень узкий плавник. По сравнению с планарными у объемных MOSFET обеспечивается бòльшая площадь поверхности стока и истока относительно поверхности канала и, следовательно, меньшее

), чем у MOSFET с тонкой базой, так как не требуется ни ультратонкая (UTB) пленка кремния, ни очень узкий плавник. По сравнению с планарными у объемных MOSFET обеспечивается бòльшая площадь поверхности стока и истока относительно поверхности канала и, следовательно, меньшее  без значительного увеличения паразитной ёмкости затвора (вследствие того, что VSTI изоляция в промежутках между полосками значительно толще, чем толщина подзатворного окисла). Это является значительным преимуществом TG bulk MOSFET, так как паразитные сопротивление и емкость все больше и больше ограничивают параметры транзистора. Исключение UTB пленки кремния или очень узких плавников также очень полезно для подавления вариаций токов в открытом и закрытом состояниях вследствие эффектов RDF.

без значительного увеличения паразитной ёмкости затвора (вследствие того, что VSTI изоляция в промежутках между полосками значительно толще, чем толщина подзатворного окисла). Это является значительным преимуществом TG bulk MOSFET, так как паразитные сопротивление и емкость все больше и больше ограничивают параметры транзистора. Исключение UTB пленки кремния или очень узких плавников также очень полезно для подавления вариаций токов в открытом и закрытом состояниях вследствие эффектов RDF.

Таким образом, преимуществами многозатворных МОПТ являются:

· подавление геометрических короткоканальных эффектов;

· малый статический ток утечки и динамическое потребление;

· высокое отношение токов в открытом и закрытом состояниях  ;

;

· совместимость с существующими технологиями изготовления;

· потенциально очень высокая степень интеграции (менее 10 нм).

Тем не менее, следует подчеркнуть, что многозатворные непланарные (3D) технологии являются технологиями скорее будущего, чем настоящего.

Литература:

1. Зебрев Г.И. Физические основы кремниевой наноэлектрники, М.: БИНОМ, 2011, с. 159-186.

2. Парменов Ю.А. Элементы твердотельной наноэлектроники. Учебное пособие. М.: МИЭТ, 2011, гл. 6.

3. Taur Y., Ning T.H., Fundamentals of Modern VLSI Device, 2009, p. 148-201.

4. Sze S.M., Ng К.К., Physics of Semiconductor Devices, Wiley, 2007, p. 293-343.

5. Taur Y., Buchanan D.A., Wei Chen, Frank D.J. at al. CMOS Scaling into the Nanometer Regime, Proceedings of the IEEE, 2001, v.85, №4, pp.486-504.

6. Liu T.-J.K. and Chang L. Transistor Scaling to the Limit, in «Into the Nano Era: Moore’s Law Beyond Planar Silicon CMOS», Ed. H. R. Huff, Springer, 2009, pp.191-223.

7. Marc Van Rossum MOS Device and Interconnects Scaling Physics, in «Advanced Nanoscale ULSI Interconnects: 15 Fundamentals and Applications», Y. Shacham-Diamand et al. (eds.), Springer Science+Business Media, pp. 15-38.

8. Helms D., Schmidt E., Nebel W. Leakage in CMOS Circuits – An Introduction. E. Macii et al. (Eds.): PATMOS 2004, LNCS 3254, pp. 17–35, 2004, Springer-Verlag Berlin Heidelberg 2004.

2014-02-10

2014-02-10 818

818