Устройство управления (УУ) предназначено для выработки управляющих сигналов, под воздействием которых происходит преобразование информации в арифметико-логическом устройстве, а также операции по записи и чтению информации в/из запоминающего устройства. Упрощенная структурная схема устройства управления (УУ) показана на рис.24.

Рис. 24 Структурная схема УУ

Основные функции УУ:

1. Формирование адреса инструкции.

2. Считывание инструкции из ОЗУ (ПЗУ) и ее хранение во время выполнения.

3. Дешифрация кода операции.

4. Формирование управляющих сигналов.

5. Считывание из регистра команд и регистров микропроцессорной памяти отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирование полных адресов операндов.

6. Выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов.

7. Запись результатов операции в память.

8. Формирования адреса следующей команды программы.

По принципу формирования и развертывания временной последовательности управляющих сигналов различают УУ:

- аппаратного (схемного) типа, выполненным в виде управляющего автомата с жесткой логикой, в котором функции переходов и выходов реализуются набором логических элементов, а требуемое количество состояний автомата задается множеством запоминающих элементов;

- микропрограммного типа, в которых блок управления реализован как блок микропрограммного управления.

По способу построения рабочего цикла различают УУ:

- с прямым циклом,

На первом этапе производится выборка из памяти команды, а затем следуют этапы выполнения машинной операции.

- с обращенным циклом,

В первую очередь выдаются управляющие сигналы для выполнения машинной операции по коду команды, поступившей в ЦУУ на предыдущем цикле (предвыборка команд), а затем из памяти выбирается код команды, которая будет исполняться в следующем цикле.

- с совмещением во времени циклов выполнения нескольких команд (конвейером команд).

По способу синхронизации работы ЭВМ в зависимости от числа тактов в цикле выполнения команды различают УУ:

- с постоянным числом тактов;

- с переменным числом тактов.

В микропрограмме рабочего цикла выделяют общую и специальную части. К общей части относятся микрокоманды, исполняемые в цикле любой команды: выборка команды, анализ запросов на прерывание, формирование адреса следующей команды, анализ состояния процессора. Эти микрокоманды выполняются за постоянное число тактов.

К специальной части относятся микрокоманды, по которым вырабатываются управляющие сигналы в зависимости от содержания операционной части исполняемой команды. В этом случае количество тактов будет переменным для различных команд. В современных ЭВМ с различной структурой используемых команд, число тактов зависит от формата выбираемой команды, структуры ее адресной части и длины операндов.

По общей организации управление может быть:

- централизованным;

- Блок управления УУ вырабатывает все УС (управляющие сигналы) микроопераций для всех команд, выполняемых процессором;

- смешанным

По принципу организации циклов различают УУ:

- синхронного типа, в которых время цикла может быть постоянным или переменным;

- асинхронного типа, в которых продолжительность цикла определяется фактическими затратами времени на выполнение каждой операции. В этом случае необходимо вырабатывать сигналы об окончании операции;

- смешанного типа, где частично реализуются оба предыдущих принципа организации циклов.

Тема 3.8. Назначение и классификация АЛУ

АЛУ – одна из основных функциональных частей процессора, осуществляющая непосредственное преобразование информации.

Все операции, выполняемые в АЛУ, можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной (шестнадцатеричной) арифметики для чисел с плавающей точкой;

- операции десятичной арифметики над числами, представленными в двоично-десятичном коде;

- операции адресной арифметики (при модификации адресов команд);

- операции специальной арифметики (нормализация, сдвиг);

- операции над алфавитно-цифровыми полями.

Для выполнения перечисленных операций в АЛУ включают следующие функциональные узлы:

- сумматор (для выполнения суммирования и других действий над кодами операндов);

- регистры (для хранения кодов операндов на время выполнения действия над ними);

- сдвигатели (для сдвига кода на один или несколько разрядов вправо или влево);

- преобразователи (для преобразования прямого кода числа в обратный или дополнительный);

- комбинационные схемы (для реализации логических операций, мультиплексирования данных, управляемой передачи информации, формирования признаков результата).

Регистры и в некоторых случаях сумматоры имеют цепи управления приемом, выдачей и сбросом кодов операндов. Логические операции, операции сдвига и преобразования кодов могут выполняться не только специальными устройствами, но и с помощью дополнительных связей регистров и сумматора.

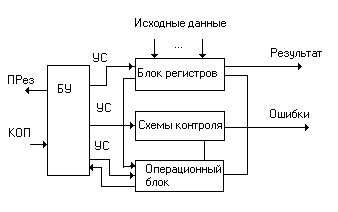

Рис.25 Структурная схема АЛУ

Обобщенная структурная схема АЛУ (рис. 25) включает:

- блок регистров (БР) для приема и размещения операндов и результатов;

- операционный блок, в котором осуществляется преобразование операндов в соответствии с реализуемыми алгоритмами;

- схемы контроля, обеспечивающие непрерывный оперативный контроль и диагностирование ошибок;

- блок управления (БУ), в котором после приема кода операции (КОП) из центрального устройства управления формируются управляющие сигналы (УС), координирующие взаимодействие всех узлов АЛУ между собой и с другими блоками процессора.

Блок регистров (БР) связан с РОН центрального процессора и кэш-памятью данных.

Иногда АЛУ не содержит своего БР, в этом случае операционный блок непосредственно работает с регистрами общего назначения процессора. Для оперативного управления выполнением операции в ОБ на разных этапах анализируется преобразуемая информация и формируются сигналы признаков (флаги), которые используются в БУ для выработки и посылки в процессор сигнала признака результата (ПРез).

2014-09-02

2014-09-02 5900

5900