В комбинационных дискретных устройствах нет ни памяти, ни временных задержек, а выход устройства в любой момент времени является функцией только входных сигналов. Возможны два подхода к диагностированию: функциональный и структурный.

При функциональном подходе устройство рассматривается как черный ящик с входами Х= {x1,..., xj} и выходами z= {z1...z K }. Каждому входному набору соответствует определенный набор выходов. Далее мы будем рассматривать устройства с одним выходом, а устройства со многими выходами будем рассматривать как набор устройств с одним выходом с объединенными входами. При этих оговорках набору { xj } соответствует выход z j - Таким образом, можно составить таблицу истинности для каждого выхода, а затем по этой таблице сделать аналитическую запись в любой формуле (СНДФ, СНКФ, скобочной или другой форме).

Но для задач диагностики функционального подхода обычно недостаточно, так как известно, что любая булева функция имеет много форм записи (даже в минимизированном виде). Поэтому для диагностирования необходим не функциональный, а структурный подход.

Компонентами структурного подхода являются конструктивно или функционально законченные блоки устройства, не подлежащие дальнейшему расщеплению. Такие блоки являются логическими элементами различной сложности с односторонней "проводимостью" (от входа к выходу) и независимостью от других блоков.

В качестве структурной модели примем так называемую правильную логическую схему (сеть), в которой выходы отделочных блоков не соединяются друг с другом. Множество функционально различных элементов устройства называется базисом {В} данной логической сети.

Итак, логическая сеть определяется множеством { ήi } логических элементов из базиса {В}, множеством входов (входных полюсов) и множеством выходов (выходных полюсов). Каждому входному полюсу соответствует входная переменная xi (i = 1,..., n), а каждому выходному полюсу - выходная переменная zj (j = l,..., k).

|

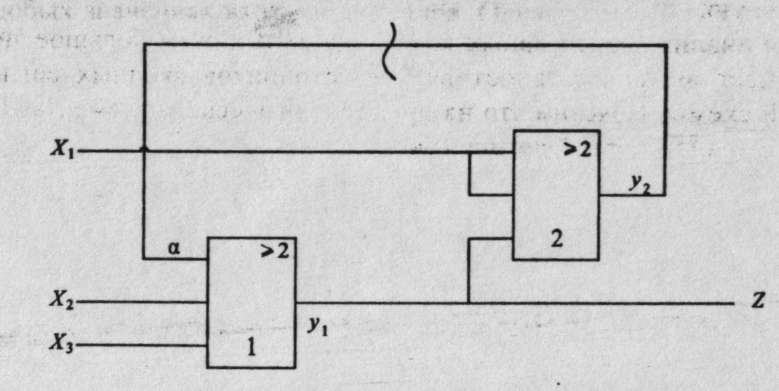

Задаются также соединения входных полюсов с входами элементов, соединения выходов одних логических элементов с входами других и выходы отдельных логических элементов с выходными полюсами. Такую сеть называют правильной. Правильная логическая сеть не исключает в ней петель или обратных связей. В качестве такого примера рассмотрим сеть, показанную на рис. 26.

Рис.26 Логическая сеть с обрывом обратной связи

Для анализа этой сети разорвем обратную связь и будем считать, что на верхний вход первого элемента подается переменная α= у2. Тогда на выходе этого элемента y1 = z = αх2 v αхз v х2xз, но y2 = α= х1 v х1y1 v х1. Отсюда следует, что z = x1х2 v x1хз v х2xз т.е. рассматриваемая сеть соответствует одному мажоритарному элементу с тремя входами.

Под неисправностью логической сети будем понимать событие, последствием которого является изменение выходной функции z = f(x1,…xn). Отметим, что некоторые неисправности логической сети таковы, что при их наличии сеть по-прежнему остается комбинационной. Однако некоторые неисправности могут привести к тому, что неисправная комбинационная сеть может превратиться из комбинационной во временную логическую сеть. При таких неисправностях методы анализа неисправностей здесь не рассматриваются.

2015-06-24

2015-06-24 461

461